SLIDE 1

Encoders Many 1-bit inputs, 1 asserted at a time. Output - - PowerPoint PPT Presentation

Encoders Many 1-bit inputs, 1 asserted at a time. Output - - PowerPoint PPT Presentation

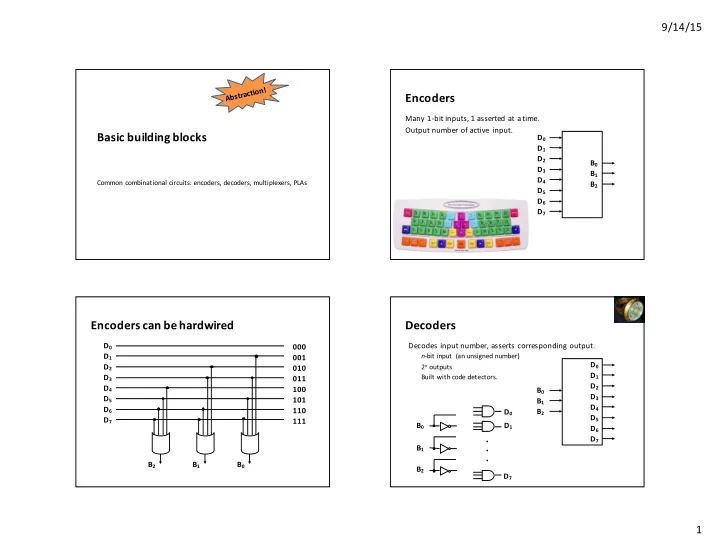

9/14/15 Encoders Many 1-bit inputs, 1 asserted at a time. Output number of active input. Basic building blocks D 0 D 1 D 2 B 0 D 3 B 1 D 4 Common combinational circuits:

SLIDE 2

SLIDE 3

9/14/15 3

MUX ¡+ ¡voltage ¡source ¡= ¡truth ¡table

D0 D1 D2 D3 D4 D5 D6 D7 F Mux A B C

A B C Majority 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Buses ¡and ¡Logic ¡Arrays

Bitwise ¡operations ¡apply ¡the ¡same ¡function ¡ to ¡each ¡bit ¡of ¡an ¡entire ¡word. A ¡bus is ¡a ¡collection ¡of ¡data ¡lines ¡that ¡is ¡ treated ¡as ¡a ¡single ¡logical ¡signal. Array ¡of ¡logic ¡elements ¡shows ¡same ¡

- peration ¡applied ¡to ¡each ¡bit ¡in ¡a ¡bus.

PLAs

A ¡programmable ¡logic ¡array (PLA) ¡has ¡a ¡ set ¡of ¡inputs ¡and ¡corresponding ¡input ¡ complements ¡and ¡two ¡stages ¡of ¡logic. The ¡first ¡state ¡is ¡an ¡array ¡of ¡AND ¡gates ¡ which ¡form ¡the ¡product ¡terms ¡ (minterms). The ¡second ¡stage ¡is ¡an ¡array ¡of ¡OR ¡gates ¡ that ¡sums ¡the ¡minterms.

Remember ¡ sum ¡of ¡products?

PLA ¡example

SLIDE 4

9/14/15 4

PLAs: ¡Another ¡drawing ¡convention

AND ¡plane: Each ¡vertical ¡ line ¡= ¡AND ¡gate. Dots ¡show ¡connected ¡inputs. OR ¡plane: Each ¡horizontal ¡line ¡= ¡OR ¡gate. Dots ¡show ¡connected ¡inputs.

As ¡a ¡ROM: input ¡= ¡address

- utput ¡= ¡contents

Gray ¡Codes ¡= ¡reflected ¡binary ¡codes

Alternate ¡ encoding ¡for ¡unsigned ¡integers designed ¡for ¡electromechanical ¡ switches ¡and ¡counting. 00 ¡ ¡ ¡01 ¡ ¡ ¡11 ¡ ¡ ¡10 000 ¡ ¡ ¡001 ¡ ¡ ¡011 ¡ ¡ ¡010 ¡ ¡ ¡110 ¡ ¡ ¡111 ¡ ¡ ¡101 ¡ ¡ ¡100 How ¡many ¡ bits ¡change ¡when ¡incrementing?

Karnaugh Maps:

find ¡minimal ¡ sums ¡of ¡products ¡visually

A B C D F(A, ¡B, ¡C, ¡D) 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

00 01 11 10 00 01 1 11 1 1 1 10 1 1 1 1 AB CD

- 1. Cover ¡exactly ¡the ¡1s ¡by ¡drawing ¡maximally ¡sized ¡rectangles ¡

whose ¡dimensions ¡(in ¡cells) ¡are ¡powers ¡of ¡2. ¡ ¡(May ¡wrap!)

- 2. For ¡each ¡box, ¡make ¡a ¡product ¡of ¡the ¡inputs ¡(or ¡complements) ¡

that ¡are ¡ 1 ¡for ¡all ¡cells ¡in ¡the ¡box. ¡(minterms)

- 3. T

ake ¡ the ¡sum ¡of ¡these ¡products.

gray ¡code

- rder