EEL7312 – INE5442 Digital Integrated Circuits 1

Dynamic operation – 20

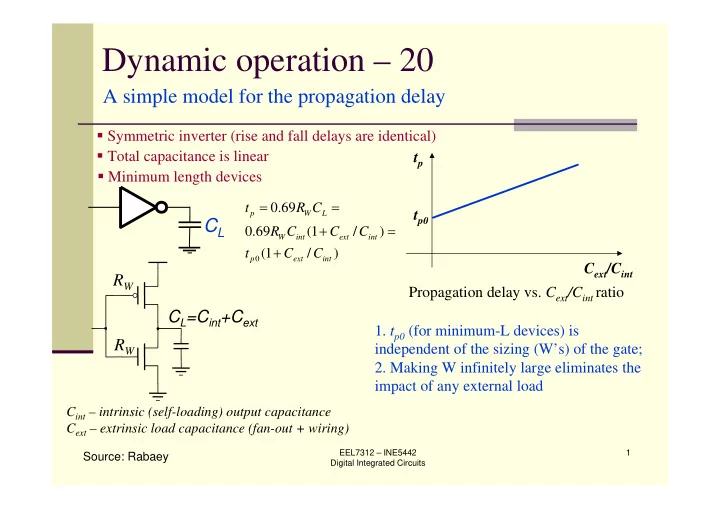

Propagation delay vs. Cext/Cint ratio

Source: Rabaey

CL

CL=Cint+Cext RW RW

Cint – intrinsic (self-loading) output capacitance Cext – extrinsic load capacitance (fan-out + wiring)

0.69 0.69 (1 / ) (1 / ) = = + = +

p W L W int ext int p ext int

t R C R C C C t C C

A simple model for the propagation delay

Symmetric inverter (rise and fall delays are identical) Total capacitance is linear Minimum length devices Cext/Cint tp tp0

- 1. tp0 (for minimum-L devices) is

independent of the sizing (W’s) of the gate;

- 2. Making W infinitely large eliminates the

impact of any external load