Dr. CU 2.0: A Scalable Detailed Routing Framework with - PowerPoint PPT Presentation

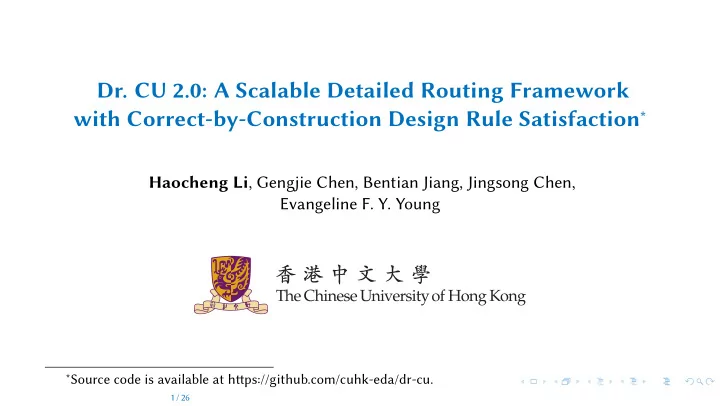

Dr. CU 2.0: A Scalable Detailed Routing Framework with Correct-by-Construction Design Rule Satisfaction Haocheng Li , Gengjie Chen, Bentian Jiang, Jingsong Chen, Evangeline F. Y. Young Source code is available at

Dr. CU 2.0: A Scalable Detailed Routing Framework with Correct-by-Construction Design Rule Satisfaction ∗ Haocheng Li , Gengjie Chen, Bentian Jiang, Jingsong Chen, Evangeline F. Y. Young ∗ Source code is available at htps://github.com/cuhk-eda/dr-cu. 1 / 26

Outline Introduction Preliminary Algorithms Experimental Results Conclusion 2 / 26

Outline Introduction Preliminary Algorithms Experimental Results Conclusion 3 / 26

Detailed Routing ◮ 1M nets in 20K × 20K × 10 grid points, hardly routed by ILP-based a or SAT-based b methods. ◮ Complicated design rules: ◮ Parallel run length (PRL) spacing c . ◮ End-of-line (EOL) spacing. ◮ EOL spacing with parallel edges d . ◮ Corner-to-corner (C2C) spacing e . a [Kahng, Wang, and Xu 2018] b [Park et al. 2019] c [Qi, Cai, and Zhou 2015] d [Yu et al. 2015] e [Côté, Pierrat, and Hurat 2004] Figure 1: Qad-Core Design [Liu et al. 2019]. 3 / 26

Problem Formulation Given ◮ technology node and design rules, ◮ placement result with netlist, ◮ routing tracks and blockages, and ◮ route guides generated from global routing, route all nets minimizing a weighted sum of ◮ total wire-length and via count, ◮ out-of-guide, off-track, wrong-way usage, and ◮ design rule violations. 4 / 26

Contributions Access Point Assignment ◮ Compute valid access points of each pin and create off-track vias if no same-layer access For Each Rip-up and Reroute Iteration point is valid. ◮ Handle end-of-line spacing with parallel edges Multi-threaded Maze Routing in a correct-by-construction manner. ◮ Fix corner-to-corner spacing violations in Multi-threaded Via Selection post-processing. ◮ Develop a lookup-table-based via insertion method and select violation-free via types from Post-routing Re fi nement the cell library. Figure 2: Detailed Routing Flow. 5 / 26

Outline Introduction Preliminary Algorithms Experimental Results Conclusion 6 / 26

Two-Level Sparse Data Structures local grid graph routing region of a net routing topology maze route record cache query edge usage global grid graph Figure 3: Global and Local Grid Graph. 6 / 26

Parallel Run Length Spacing w 2 R2 The parallel run length (PRL) s t R2 l t spacing requirements between two s m wires of different nets depend on s b both width and PRL of the two w 1 R1 wires. l b R2 Figure 4: Parallel Run Length Spacing. 7 / 26

End-of-line Spacing Figure 5: Example of Triple Paterning Layout Decomposition † . eolWithin parWithin parSpace Metal Metal Parallel eolWidth eolWidth Edge Region eolWithin eolWithin EOL Spacing EOL Spacing eolSpace eolSpace Figure 7: EOL Spacing with Parallel Edges. Figure 6: EOL Spacing without Parallel Edges. † [Yu et al. 2015] 8 / 26

<latexit sha1_base64="Xjl2NlYS/IYscB7kNQ47CiBlpoA=">AB+XicbVBNS8NAEN34WetX1KOXxVbwVJe7LHgxWMF+wFtKJvNpF262Q27m0oJ/SdePCji1X/izX/jts1BWx8MPN6bYWZemHKmjed9O1vbO7t7+6WD8uHR8cmpe3be0TJTFNpUcql6IdHAmYC2YZDL1VAkpBDN5zcLfzuFJRmUjyaWQpBQkaCxYwSY6Wh61af8IADBsm7LDLj6tCteDVvCbxJ/IJUIHW0P0aRJmCQhDOdG673upCXKiDKMc5uVBpiEldEJG0LdUkAR0kC8vn+Nrq0Q4lsqWMHip/p7ISaL1LAltZ0LMWK97C/E/r5+ZuBHkTKSZAUFXi+KMYyPxIgYcMQXU8JklhCpmb8V0TBShxoZVtiH46y9vk695ns1/6FeaTaKOEroEl2hG+SjW9RE96iF2oiKXpGr+jNyZ0X5935WLVuOcXMBfoD5/MHLd6Sqw=</latexit> <latexit sha1_base64="Xjl2NlYS/IYscB7kNQ47CiBlpoA=">AB+XicbVBNS8NAEN34WetX1KOXxVbwVJe7LHgxWMF+wFtKJvNpF262Q27m0oJ/SdePCji1X/izX/jts1BWx8MPN6bYWZemHKmjed9O1vbO7t7+6WD8uHR8cmpe3be0TJTFNpUcql6IdHAmYC2YZDL1VAkpBDN5zcLfzuFJRmUjyaWQpBQkaCxYwSY6Wh61af8IADBsm7LDLj6tCteDVvCbxJ/IJUIHW0P0aRJmCQhDOdG673upCXKiDKMc5uVBpiEldEJG0LdUkAR0kC8vn+Nrq0Q4lsqWMHip/p7ISaL1LAltZ0LMWK97C/E/r5+ZuBHkTKSZAUFXi+KMYyPxIgYcMQXU8JklhCpmb8V0TBShxoZVtiH46y9vk695ns1/6FeaTaKOEroEl2hG+SjW9RE96iF2oiKXpGr+jNyZ0X5935WLVuOcXMBfoD5/MHLd6Sqw=</latexit> <latexit sha1_base64="tTCwZFMox0LwI3sFQk9NA4SxyU=">AB9XicbVA9SwNBEN3zM8avqKXNYiJYhbs0pKAjWUE8wHJGfb25pIle7vH7p4hHPkfNhaK2Ppf7Pw3bpIrNPHBwO9GWbmBQln2rjut7OxubW9s1vYK+4fHB4dl05O21qmikKLSi5VNyAaOBPQMsxw6CYKSBxw6ATj27nfeQKlmRQPZpqAH5OhYBGjxFjpsTLBNxgk7DQjCqDUtmtugvgdeLlpIxyNAelr34oaRqDMJQTrXuemxg/I8owymFW7KcaEkLHZAg9SwWJQfvZ4uoZvrRKiCOpbAmDF+rviYzEWk/jwHbGxIz0qjcX/N6qYnqfsZEkhoQdLkoSjk2Es8jwCFTQA2fWkKoYvZWTEdEWpsUEUbgrf68jp16qeW/Xua+VGPY+jgM7RBbpCHrpGDXSHmqiFKFLoGb2iN2fivDjvzseydcPJZ87QHzifP/WzkXc=</latexit> <latexit sha1_base64="tTCwZFMox0LwI3sFQk9NA4SxyU=">AB9XicbVA9SwNBEN3zM8avqKXNYiJYhbs0pKAjWUE8wHJGfb25pIle7vH7p4hHPkfNhaK2Ppf7Pw3bpIrNPHBwO9GWbmBQln2rjut7OxubW9s1vYK+4fHB4dl05O21qmikKLSi5VNyAaOBPQMsxw6CYKSBxw6ATj27nfeQKlmRQPZpqAH5OhYBGjxFjpsTLBNxgk7DQjCqDUtmtugvgdeLlpIxyNAelr34oaRqDMJQTrXuemxg/I8owymFW7KcaEkLHZAg9SwWJQfvZ4uoZvrRKiCOpbAmDF+rviYzEWk/jwHbGxIz0qjcX/N6qYnqfsZEkhoQdLkoSjk2Es8jwCFTQA2fWkKoYvZWTEdEWpsUEUbgrf68jp16qeW/Xua+VGPY+jgM7RBbpCHrpGDXSHmqiFKFLoGb2iN2fivDjvzseydcPJZ87QHzifP/WzkXc=</latexit> Corner-to-Corner Spacing w ≤ eolWidth <latexit sha1_base64="Xjl2NlYS/IYscB7kNQ47CiBlpoA=">AB+XicbVBNS8NAEN34WetX1KOXxVbwVJe7LHgxWMF+wFtKJvNpF262Q27m0oJ/SdePCji1X/izX/jts1BWx8MPN6bYWZemHKmjed9O1vbO7t7+6WD8uHR8cmpe3be0TJTFNpUcql6IdHAmYC2YZDL1VAkpBDN5zcLfzuFJRmUjyaWQpBQkaCxYwSY6Wh61af8IADBsm7LDLj6tCteDVvCbxJ/IJUIHW0P0aRJmCQhDOdG673upCXKiDKMc5uVBpiEldEJG0LdUkAR0kC8vn+Nrq0Q4lsqWMHip/p7ISaL1LAltZ0LMWK97C/E/r5+ZuBHkTKSZAUFXi+KMYyPxIgYcMQXU8JklhCpmb8V0TBShxoZVtiH46y9vk695ns1/6FeaTaKOEroEl2hG+SjW9RE96iF2oiKXpGr+jNyZ0X5935WLVuOcXMBfoD5/MHLd6Sqw=</latexit> <latexit sha1_base64="Xjl2NlYS/IYscB7kNQ47CiBlpoA=">AB+XicbVBNS8NAEN34WetX1KOXxVbwVJe7LHgxWMF+wFtKJvNpF262Q27m0oJ/SdePCji1X/izX/jts1BWx8MPN6bYWZemHKmjed9O1vbO7t7+6WD8uHR8cmpe3be0TJTFNpUcql6IdHAmYC2YZDL1VAkpBDN5zcLfzuFJRmUjyaWQpBQkaCxYwSY6Wh61af8IADBsm7LDLj6tCteDVvCbxJ/IJUIHW0P0aRJmCQhDOdG673upCXKiDKMc5uVBpiEldEJG0LdUkAR0kC8vn+Nrq0Q4lsqWMHip/p7ISaL1LAltZ0LMWK97C/E/r5+ZuBHkTKSZAUFXi+KMYyPxIgYcMQXU8JklhCpmb8V0TBShxoZVtiH46y9vk695ns1/6FeaTaKOEroEl2hG+SjW9RE96iF2oiKXpGr+jNyZ0X5935WLVuOcXMBfoD5/MHLd6Sqw=</latexit> w ≤ eolWidth w > eolWidth <latexit sha1_base64="tTCwZFMox0LwI3sFQk9NA4SxyU=">AB9XicbVA9SwNBEN3zM8avqKXNYiJYhbs0pKAjWUE8wHJGfb25pIle7vH7p4hHPkfNhaK2Ppf7Pw3bpIrNPHBwO9GWbmBQln2rjut7OxubW9s1vYK+4fHB4dl05O21qmikKLSi5VNyAaOBPQMsxw6CYKSBxw6ATj27nfeQKlmRQPZpqAH5OhYBGjxFjpsTLBNxgk7DQjCqDUtmtugvgdeLlpIxyNAelr34oaRqDMJQTrXuemxg/I8owymFW7KcaEkLHZAg9SwWJQfvZ4uoZvrRKiCOpbAmDF+rviYzEWk/jwHbGxIz0qjcX/N6qYnqfsZEkhoQdLkoSjk2Es8jwCFTQA2fWkKoYvZWTEdEWpsUEUbgrf68jp16qeW/Xua+VGPY+jgM7RBbpCHrpGDXSHmqiFKFLoGb2iN2fivDjvzseydcPJZ87QHzifP/WzkXc=</latexit> <latexit sha1_base64="tTCwZFMox0LwI3sFQk9NA4SxyU=">AB9XicbVA9SwNBEN3zM8avqKXNYiJYhbs0pKAjWUE8wHJGfb25pIle7vH7p4hHPkfNhaK2Ppf7Pw3bpIrNPHBwO9GWbmBQln2rjut7OxubW9s1vYK+4fHB4dl05O21qmikKLSi5VNyAaOBPQMsxw6CYKSBxw6ATj27nfeQKlmRQPZpqAH5OhYBGjxFjpsTLBNxgk7DQjCqDUtmtugvgdeLlpIxyNAelr34oaRqDMJQTrXuemxg/I8owymFW7KcaEkLHZAg9SwWJQfvZ4uoZvrRKiCOpbAmDF+rviYzEWk/jwHbGxIz0qjcX/N6qYnqfsZEkhoQdLkoSjk2Es8jwCFTQA2fWkKoYvZWTEdEWpsUEUbgrf68jp16qeW/Xua+VGPY+jgM7RBbpCHrpGDXSHmqiFKFLoGb2iN2fivDjvzseydcPJZ87QHzifP/WzkXc=</latexit> w > eolWidth Figure 8: C2C spacing does not apply. Figure 9: C2C spacing applies. 9 / 26

Outline Introduction Preliminary Algorithms Experimental Results Conclusion 10 / 26

Local Grid Graph Construction Metal 1 Metal 2 ◮ Expand route guides in preferred routing direction for full connections. ◮ Expand in x - and y -direction for each rip-up-and-reroute iteration. ◮ Extend to adjacent layers if the (a) Before Expansion. (b) Afer Expansion. numbers of violations exceed a threshold. Figure 10: Unconnected Route Guides. 10 / 26

Pin Access ◮ Assign same-layer surrounding grid points as access points by default. ◮ Use diff-layer access points by an off-track via if no valid same-layer access points. ◮ Penalize other nets for using grid points above/below it before it is connected. OBS OBS D D SI SI SE SE Figure 11: No valid same-layer access point. Figure 12: Use off-track via 11 / 26

Via Type Selection Flow LUT Construction For Each Rip-up and Reroute Iteration ◮ Construct via conflict lookup tables (LUTs). ◮ Determine via locations and generate routing Multi-threaded Via Locationing topology for a net. ◮ Perform via type selection for the net. Multi-threaded Type Selection ◮ Finally decide via type globally in a post refinement stage. Post-routing Type Selection Figure 13: Detailed Routing Flow. 12 / 26

Via Conflict Lookup Table M3 track M4 track candidate via using via type 1 ◮ Via-pin/obstacle conflicts. neighboring via using via type 2 ◮ Via-wire conflicts. conflict w.r.t. neighboring via using via type 2 ◮ Via-via conflicts. violation-free locations forbidden locations/region Figure 14: Via-via LUT. 13 / 26

Pessimistic Lookup Table M3 track ◮ Checking every via-type M4 track during routing is candidate via using via type 1 time-consuming. conflict w.r.t. via using via type 1 ◮ Merged LUTs records all conflict w.r.t. via using via type 2 suspicious conflicts. conflict w.r.t. via using via type 3 ◮ Suspicious conflicts can be violation-free locations verified when the via types forbidden regions union are determined. Figure 15: Merged Via-via LUT. 14 / 26

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.