Digital IC Design

Design Methodologies

Viktor Öwall Viktor Öwall

- Dept. of Electrical and Infomation Technology

Lund University Lund University

Parts of this material was adapted from the instructor material to Jan M. Rabaey, Digital Integrated Circuits: A

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

material to Jan M. Rabaey, Digital Integrated Circuits: A Design Perspective, Prentice Hall International Editions Digital IC Design

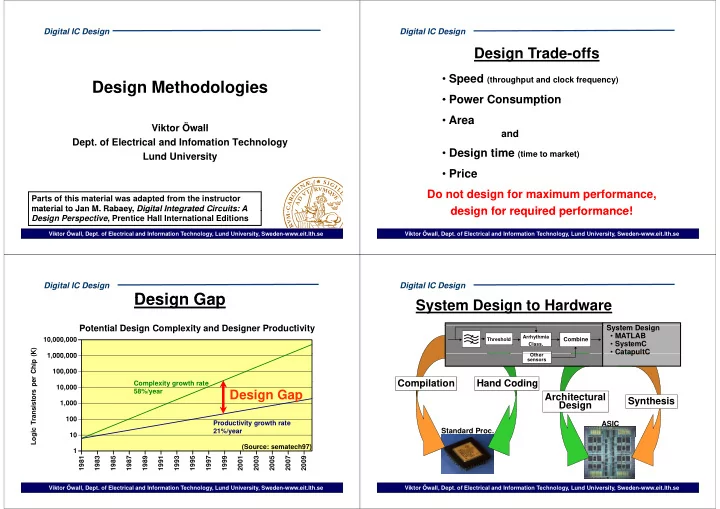

Design Trade-offs

- Speed (throughput and clock frequency)

- Power Consumption

- Power Consumption

- Area

and

- Design time (time to market)

Design time (time to market)

- Price

Do not design for maximum performance, design for required performance!

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

design for required performance!

Digital IC Design

Design Gap Design Gap

P t ti l D i C l it d D i P d ti it

1 000 000 10,000,000

Potential Design Complexity and Designer Productivity

K) 1,000,000 100,000 C l it th t er Chip (K 1,000 10,000 Complexity growth rate 58%/year sistors pe

Design Gap

10 100 Productivity growth rate 21%/year

- gic Trans

981 991 989 987 985 983 001 999 997 995 993 009 007 005 003 1 Lo (Source: sematech97)

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se

19 19 19 19 19 19 20 19 19 19 19 20 20 20 20

Digital IC Design

System Design to Hardware

S t D i

Arrhythmia Class.

Combine

Oth Threshold

System Design

- MATLAB

- SystemC

- CatapultC

Other sensors

Compilation Hand Coding

CatapultC

Compilation Hand Coding Architectural Design Synthesis g

Standard Proc. ASIC

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden-www.eit.lth.se