Design and Architectures for Embedded Systems Prof. Dr. J. Henkel - PDF document

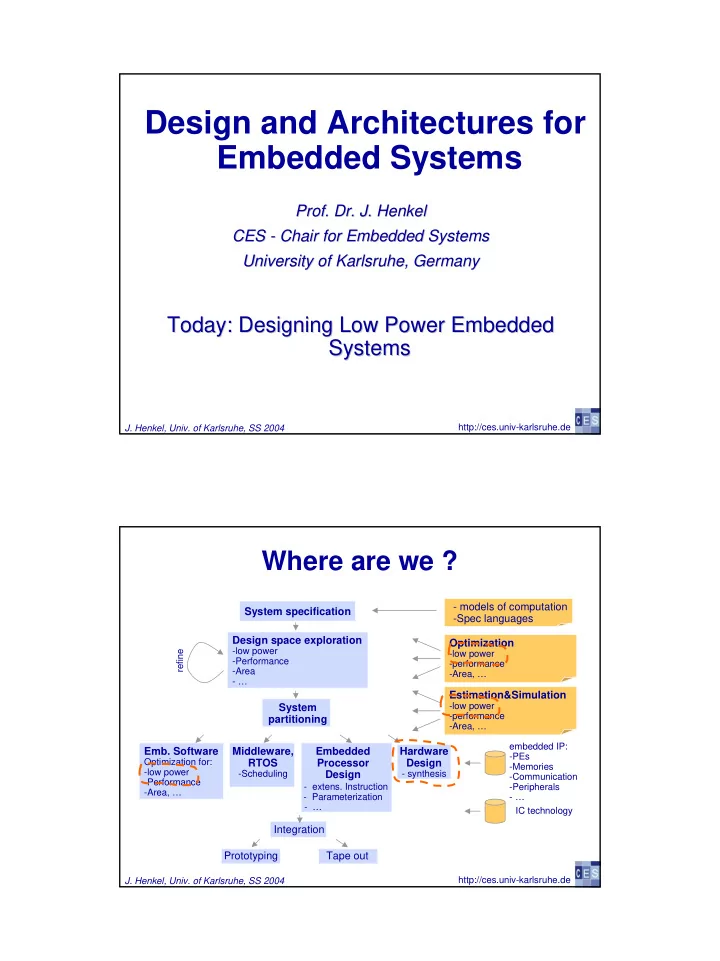

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES CES - - Chair for Embedded Systems Chair for Embedded Systems University of University of Karlsruhe Karlsruhe, Germany , Germany Today: Designing

Design and Architectures for Embedded Systems Prof. Dr. J. Henkel Henkel Prof. Dr. J. CES CES - - Chair for Embedded Systems Chair for Embedded Systems University of University of Karlsruhe Karlsruhe, Germany , Germany Today: Designing Low Power Embedded Today: Designing Low Power Embedded Systems Systems http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Where are we ? - models of computation System specification -Spec languages Design space exploration Optimization -low power refine -low power -Performance -performance -Area -Area, … - … Estimation&Simulation -low power System -performance partitioning -Area, … embedded IP: Emb. Software Middleware, Embedded Hardware -PEs Optimization for: RTOS Processor Design -Memories -low power -Scheduling Design - synthesis -Communication -Performance - extens. Instruction -Peripherals -Area, … - Parameterization - … - … IC technology Integration Prototyping Tape out http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

(Src: F. Pollack, Intel http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Low Power/Energy: Reason Portable Systems � Thermal Considerations � � Notebooks, palm-tops, PDA, 10 o C increase in operating � cellular phones, pagers, etc. temperature => component 32% of PC market, and growing � failure rate doubles � Battery-driven - long battery life � Packaging: ceramic vs . plastic crucial � Cooling requirements � System cost, weight limited by batteries Increasing levels of � 40W, 10 hrs @ 20-35 W- � integration / clock hr/pound = 7-20 pounds (Src: A. Raghunathan, NEC) frequencies make the Slow growth in battery � technology problem worse Must reduce energy drain � LOW 10cm 2 , 500 MHz => 315Watts � from batteries POWER Reliability Issues � Environmental Concerns � � Electro-migration � IR drops on supply lines � EPA estimate: 80% of office equipment electricity is used � Inductive effects in computers Tied to peak/average � � “Energy Star” program to power consumption recognize power efficient PCs � Power management standard for desktops and laptops Drive towards “Green PC” � http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

Power Consumption and flexibility Operations/Watt [MOPS/mW] Ambient Intelligence 10 ) C DSP-ASIPs I S A g n ( d t i u e p r m s i r 1 w o o d C s s r e e a b l o c h r a P µPs r u g f i n o c e R 0.1 poor design generation 0.01 techniques Technology 1.0µ 0.5µ 0.25µ 0.13µ 0.07µ (Src:[Marw03]) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Power Sources Energy Source Power/Energy Density 1050-1560 mWh/cm 3 Batteries (Zinc-Air, primary) 300 mWh/cm 3 Batteries (Li, rechargeable) 15 mW/cm 2 (direct sun) Solar (outdoors) 1 mW/cm 2 (24 hour avg) 0.006 mW/cm 2 (office desk) Solar (indoors) 0.57mW/cm 2 (<60W desk lamp) Vibrations 0.01-0.1 mW/cm 3 3 e-6 mW/cm 2 @ 75dB Acoustic (noise) 9.6 e-4 mW/cm 2 @ 100dB Non-inertial Human Power 1.8 mW (shoe inserts) 80 mW/cm 3 , 1 e+6 mWh/cm 3 Nuclear Reaction (Src: A. Raghunathan, NEC) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

Relationship between Power and Energy P E t ∫ = E P dt http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Power vs. Energy � Minimizing the power consumption is important for � the design of the power supply � the design of voltage regulators � the dimensioning of interconnect � short term cooling � Minimizing the energy consumption: � Limited availability of energy (mobile systems, try to maximize the amount of computation that can be accomplished with a given amount of energy) through: � limited battery capacities (only slowly improving) � very high costs of energy (solar panels, in space) � cooling � high costs � limited space � dependability � long lifetimes, low temperatures (Src:[Marw03]) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

Power by Processor Type Pentium Crusoe Pentium 4 Crusoe Processor (source: www.transmeta.com) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Outline � System � System- -level Design Methodologies level Design Methodologies System- System -level power estimation level power estimation � � Low- Low -power Embedded Software power Embedded Software � � System- System -level Tradeoffs and Power Management level Tradeoffs and Power Management � � (src: A. Raghunathan, NEC) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

Hardware-Software System Design and Validation Flow VALIDATION SYSTEM SPEC Cores ESTIMATORS MAPPING / PARTITIONING - TIMING MPU, MCU,DSP C-MODELS, - POWER ALGORITHMIC Peripherals HDL- CO-VALIDATION MODELS Interface S/W App. Multimedia HARD SOFT Spec TASKS CORES CORES H/W Telecom/ CPU Networking CYCLE S/W H/W BASED IMPLEMENTATION ARCHITECTURAL SYNTHESIS - ISS CO-VALIDATION - HDL DFT & TEST ASIC BUS DFT & TEST GENERATION INTEGRATION ARCHITECTURE GENERATION CPU Co- UDL FULL FULL CORE proc. TIMING TIMING MODELS VERIFICATION ROM/ Periph. PCI/ RAM MPEG PROTOTYPE (src: A. Raghunathan, NEC) ASIC PROTOTYPE VERIFICATION Embedded Software Implementation and Validation Software Tasks Estimators - Performance - Power Instruction Set Mapping tasks to CPUs Compiler Simulator Assembler Linker Multitask Scheduling - Priority selection Co-Simulator H /W Multiprocessor Integration Debugger RTOS - Protocols Emulator - Shared Memory Software Implementation (src: A. Raghunathan, NEC)

Outline � � System System- -level Design Methodologies level Design Methodologies System- System -level power estimation level power estimation � � Low- Low -power Embedded Software power Embedded Software � � System- System -level Tradeoffs and Power Management level Tradeoffs and Power Management � � (src: A. Raghunathan, NEC) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 System-level power estimation: summary � Background � Background � � Power estimation in HW design Power estimation in HW design � Embedded SW power estimation � Embedded SW power estimation � System � System- -level estimation approaches level estimation approaches � The spreadsheet approach � The spreadsheet approach � Power state machines � Power state machines � � HW/SW co HW/SW co- -simulation simulation � � Battery modeling Battery modeling http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

HW Power Estimation: Overview 1 ) ( 2 = Power Cap Switching Power . 2 C . . V . A f . L dd + Short Ckt Power . Leakage/Static Power High-level synthesis, Power analysis RTL optimizations iteration times Architecture-level Power models Decreasing design iteration times power analysis for macroblocks, seconds - minutes control logic Behavior level Logic synthesis Register-transfer level Power models Logic-level minutes - hours for gates, cells, power analysis nets Transistor-level/ Logic level Layout synthesis hours - days Transistor-level Transistor level power analysis (src: A. Raghunathan, NEC) http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004 Instruction-level SW power modeling � Energy consumed = f(Instruction sequence) � Energy consumed = f(Instruction sequence) � Model using � Model using per per- -instruction costs instruction costs , , circuit state overhead costs circuit state overhead costs , and , and penalties for pipeline stalls and cache misses penalties for pipeline stalls and cache misses Program energy cost = � Program � energy cost = Σ I Σ ) + Σ Σ I,J (Base I x N I (Ovhd Ovhd I,J x N I,J ) + I (Base I x N I ) + I,J ( I,J x N I,J ) + Ν CM Ν CM ∗ ∗ Penalty CM + + Ν Ν Stall Stall ∗ ∗ Penalty Penalty CM Penalty Stall Stall N I N : Number of times instruction I is executed : Number of times instruction I is executed I Base I Base : Base energy cost of I (ignores stalls,cache misses) : Base energy cost of I (ignores stalls,cache misses) I Ovhd I,J Ovhd I,J : Circuit state overhead when I, J are adjacent : Circuit state overhead when I, J are adjacent CM : : Cache Miss Penalty Penalty CM Penalty Cache Miss Penalty Stall : : Pipeline Stall Penalty Penalty Stall Penalty Pipeline Stall Penalty � Circuit state overhead: depends on processor architecture � Circuit state overhead: depends on processor architecture � Constant value for 486DX2, Fujitsu � Constant value for 486DX2, Fujitsu SPARClite SPARClite � Table for Fujitsu DSP due to greater variation � (src: A. Raghunathan, NEC) Table for Fujitsu DSP due to greater variation [Tiwari94c,Tiwari96] http://ces.univ-karlsruhe.de J. Henkel, Univ. of Karlsruhe, SS 2004

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.