SLIDE 30 Core Formation

ONNET

Routers Organization Packet Switching Input/Output Packetization Address Decoding Destination ID Buffer Size Output Data Size HLFU ID Path Latency Destination Router ID Type of MIN Input Traffic HLFU Count Logical Grouping Buffer/ Stack Size Route Location Data Rate I/O Port

Decoders Decodin g Rate Length

Packet Size I/P Data Size Word Length

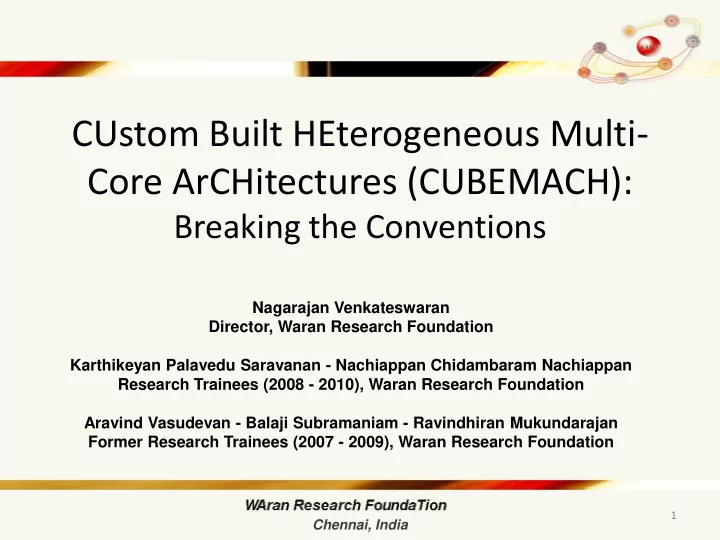

CUBEMACH Architectural Space

Multiple Applications Multiple Applications Multiple Applications Input Power Model Performance Model Desired Power to Performance Ratio

CUBEMACH Optimization Space CUBEMACH Simulation Space

Game Theory Simulated Annealing Selected Parameters Simulator Simulation Results Intermediate Architectural Parameters Final CUBEMACH Calculated Power to Performance Ratio Initial Candidate Architecture Parameters SCOS PCOS

parallel Units Rate of Output Generation Scheduler Processing rate

Ports BISA Length

I/O Ports Scheduler O/P Generation rate

Compiler-On-Silicon

Control Unit Algorithm Size Memory In Processor HLFU Characteristics ALFU Requirements Delay ALFU Types Class of Algorithms Type of MIP Cell Number

Cells HLFU Control Centralize/ Decentralized Grain Size Architecture Class of Units Input Bits Scalar

ALFU SRAM DRAM

Mapping and Replacement Heuristic Packet Size No of Blocks DRAM Size SRAM Size Cache Line Size Word Length

Memory

No Of Ports Number of Instructions Per ALISA Types of Instructions Per ALISA Types of Instructions in ISA

ALISA

No of ALISA Fields Decoding/ Encoding Logic Field Length

30