1

CALTECH CS137 Winter2006 -- DeHon 1

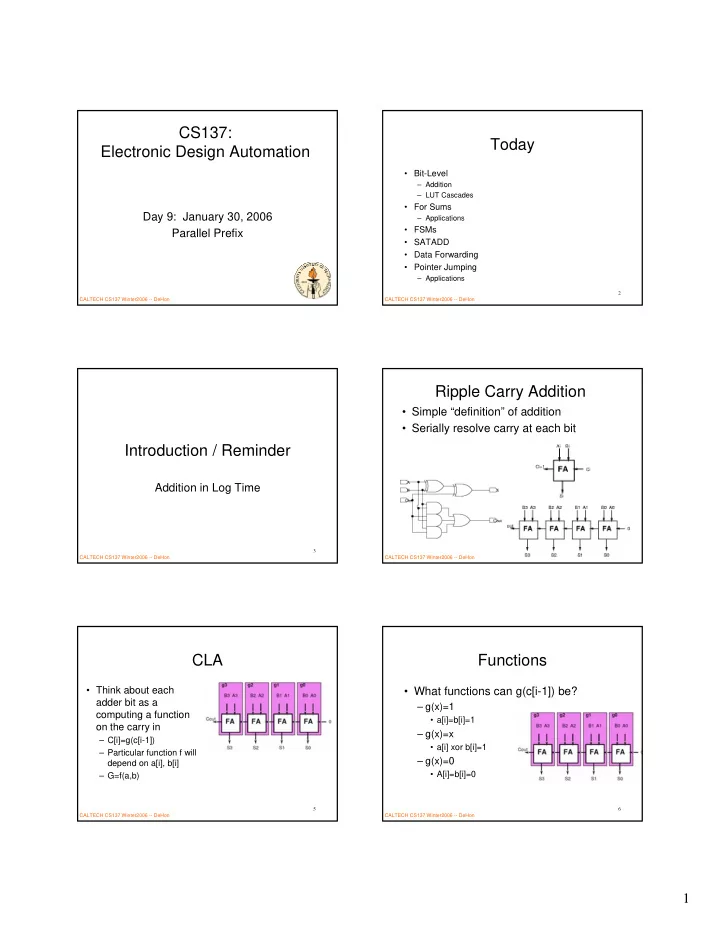

CS137: Electronic Design Automation

Day 9: January 30, 2006 Parallel Prefix

CALTECH CS137 Winter2006 -- DeHon 2

Today

- Bit-Level

– Addition – LUT Cascades

- For Sums

– Applications

- FSMs

- SATADD

- Data Forwarding

- Pointer Jumping

– Applications

CALTECH CS137 Winter2006 -- DeHon 3

Introduction / Reminder

Addition in Log Time

CALTECH CS137 Winter2006 -- DeHon 4

Ripple Carry Addition

- Simple “definition” of addition

- Serially resolve carry at each bit

CALTECH CS137 Winter2006 -- DeHon 5

CLA

- Think about each

adder bit as a computing a function

- n the carry in

– C[i]=g(c[i-1]) – Particular function f will depend on a[i], b[i] – G=f(a,b)

CALTECH CS137 Winter2006 -- DeHon 6

Functions

- What functions can g(c[i-1]) be?

– g(x)=1

- a[i]=b[i]=1

– g(x)=x

- a[i] xor b[i]=1

– g(x)=0

- A[i]=b[i]=0