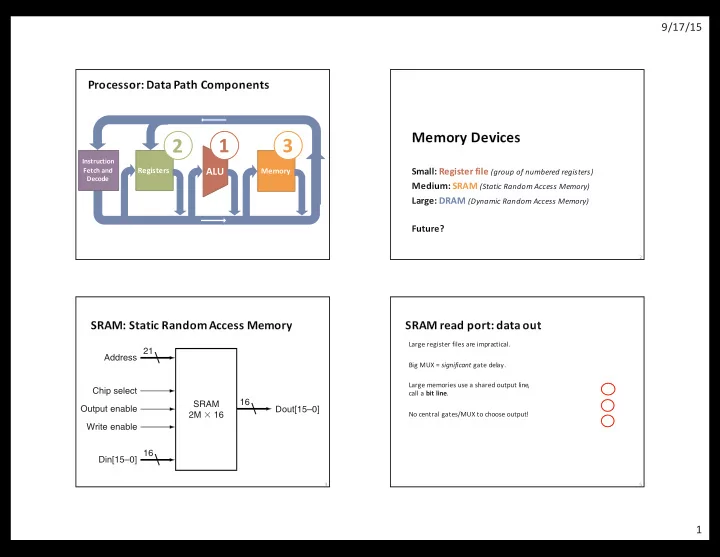

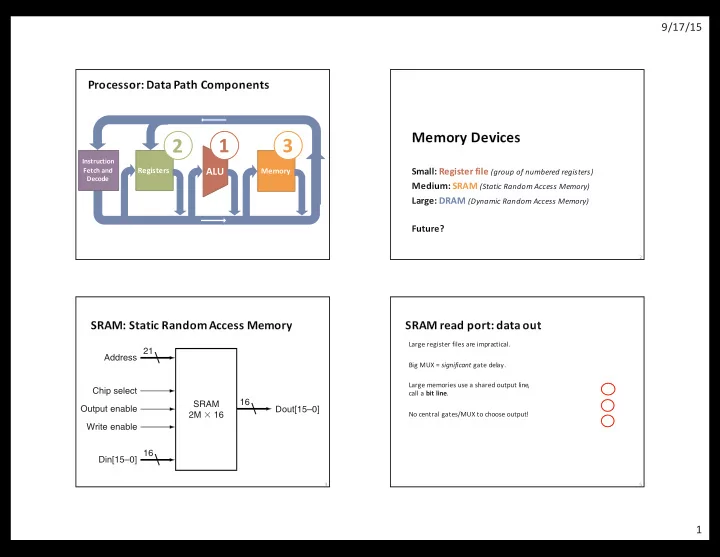

9/17/15 Processor: ¡Data ¡Path ¡Components Memory ¡Devices 2 1 3 Instruction ¡ ALU Registers Small: ¡Register ¡file (group ¡of ¡numbered ¡registers) Fetch and ¡ Memory Decode Medium: ¡SRAM (Static ¡Random ¡Access ¡Memory) Large: ¡DRAM (Dynamic ¡Random ¡Access ¡Memory) Future? 2 SRAM: ¡Static ¡Random ¡Access ¡Memory SRAM ¡read ¡port: ¡data ¡out Large ¡register ¡files ¡are ¡impractical. Address 21 Big ¡MUX ¡= ¡ significant gate ¡delay. Large ¡memories ¡use ¡a ¡shared ¡output ¡line, ¡ Chip select call ¡a ¡ bit ¡line . 16 SRAM Output enable Dout[15–0] No ¡central ¡gates/MUX ¡to ¡choose ¡output! 2M 3 16 Write enable Din[15–0] 16 3 5 1

9/17/15 (noninverting) tristate buffers Wired ¡ORs (don't ¡try ¡this ¡at ¡home/in ¡the ¡lab, ¡kids) Out In Control In Control Out 0 0 Z Danger , ¡ Will ¡Robinson! 1 0 Z 0 1 0 1 1 1 6 7 Data ¡in: D in [1] Din[1] D in [0] Din[1] SRAM ¡cell SRAM ¡write ¡port: D D one ¡option D D C latch Q C latch Q Write ¡enable Write enable Enable Enable Tristate ¡Buffer 0 0 Address 2-to-4 D D D D decoder C Q C Q latch latch D Enable Enable D Q 1 1 2-‑to-‑4 ¡decoder D Latch D in [i] D out [i] Q D D D D C C latch Q C latch Q C Q Address D Enable Enable D C Q 2 latch 2 Enable Enable Address D D D D C Q C Q latch latch Select Enable Enable Write ¡ 3 3 enable Data ¡out: D out [1] D out [0] 9 Dout[1] Dout[0] 8 2

9/17/15 Organization ¡of ¡a ¡16 ¡x ¡4 ¡SRAM Selecting ¡location ¡1101 (one ¡option) 4-‑bit 4-‑bit address address 1101 4 ¡to ¡16 4 ¡to ¡16 decoder decoder data data out out But ¡should ¡we ¡build ¡a ¡32 ¡to ¡2 32 decoder? 10 11 Another ¡organization ¡of ¡a ¡16 ¡x ¡4 ¡SRAM Selecting ¡location ¡0010 Nibbles ¡"striped" ¡across ¡4 ¡smaller ¡memories. Split-‑level ¡row/column ¡addressing ¡= ¡physical ¡multidimensional ¡array! top top 2 ¡bits 2 ¡bits (row) (row) address address 2 ¡to ¡4 2 ¡to ¡4 decoder decoder 00 2 10 2 bottom bottom 2 ¡bits 2 ¡bits address address Mux Mux Mux Mux Mux Mux Mux Mux (column) (column) 4 0010 12 13 3

9/17/15 Selecting ¡location ¡1101 What ¡value ¡does ¡location ¡1010 ¡hold? Nibbles ¡"striped" ¡across ¡4 ¡smaller ¡memories. top 2 ¡bits 0 1 1 1 0 1 0 0 1 0 0 0 0 0 1 1 (row) address 2 ¡to ¡4 2 ¡to ¡4 1 0 0 0 0 1 1 0 1 0 0 1 0 0 0 1 1 1 0 0 0 1 0 1 1 1 0 1 1 1 0 1 decoder decoder 0 1 1 0 1 0 0 0 0 0 0 1 1 1 1 1 11 2 01 2 2 2 bottom 2 ¡bits address Mux Mux Mux Mux Mux Mux Mux Mux 4 4 (column) 1101 1010 14 15 Word line Organization ¡of ¡a ¡4M ¡x ¡8 ¡SRAM (one ¡option) Pass transistor = ¡4 ¡MB ¡memory, ¡size ¡of ¡a ¡large ¡cache ¡for ¡modern ¡laptop Capacitor 4K � 4K � 4K � 4K � 4K � 4K � 4K � 4K � Dynamic ¡RAM ¡= ¡DRAM 1024 1024 1024 1024 1024 1024 1024 1024 SRAM SRAM SRAM SRAM SRAM SRAM SRAM SRAM 12 4096 Address to Bit line [21–10] 4096 DRAM ¡ stores ¡bit ¡as ¡charge ¡on ¡capacitor: decoder • 1 ¡transistor ¡ ¡accesses ¡stored ¡charge. • requires ¡periodic ¡refresh ¡= ¡read-‑write ¡ 1024 Address (dynamic ¡power) [9–0] Mux Mux Mux Mux Mux Mux Mux Mux SRAM stores ¡bit ¡on ¡pair ¡of ¡inverting ¡gates: • several ¡transistors Dout7 Dout6 Dout5 Dout4 Dout3 Dout2 Dout1 Dout0 • requires ¡continuous ¡(static) ¡power. In ¡practice, ¡single ¡set ¡of ¡data ¡lines ¡often ¡time-‑shared ¡for ¡read ¡(out)/write ¡(in). 16 17 4

9/17/15 DRAM ¡design 64-‑bit ¡DRAM (one ¡option) Row 2048 � 2048 decoder array 3 ¡to ¡8 11-to-2048 row decoder Address[10–0] Column latches Single ¡set ¡of ¡address ¡lines, 3-‑bit ¡ Column ¡latches address time-‑shared ¡for ¡row ¡address, ¡column ¡address. Mux Mux Accesses ¡entire ¡row, ¡stores ¡in ¡column ¡latches. Mainly ¡used ¡for ¡refreshing ¡entire ¡row ¡at ¡a ¡time. Dout Accessing ¡other ¡columns ¡in ¡same ¡row ¡again ¡cheaper...? Data ¡ out 18 19 Reading ¡bit ¡at ¡address ¡101011 Reading ¡bit ¡at ¡address ¡101011 1. ¡Select ¡row 2. ¡Copy ¡row ¡to ¡latches 3 ¡to ¡8 3 ¡to ¡8 row row decoder decoder Row ¡is ¡fading! 101 101 Column ¡latches Column ¡latches 3-‑bit ¡ 3-‑bit ¡ address address Mux Mux Data ¡ out Data ¡ out 20 21 5

9/17/15 Reading ¡bit ¡at ¡address ¡101011 Reading ¡bit ¡at ¡address ¡101011 3. ¡Refresh ¡row ¡from ¡latches 4. ¡Select ¡column ¡from ¡latches 3 ¡to ¡8 3 ¡to ¡8 row row decoder decoder Refresh. 101 011 Column ¡latches Column ¡latches 3-‑bit ¡ 3-‑bit ¡ address address Mux Mux Data ¡ out Data ¡ out 22 23 6

Recommend

More recommend