UMBC A B M A L T F O U M B C I M Y O R T 1 (Apr. - PowerPoint PPT Presentation

Systems Design and Programming Basic I/O II CMPE 310 Programmable Peripheral Interface ( 82C55) The 82C55 is a popular interfacing component, that can interface any TTL- compatible I/O device to the microprocessor. It is used to interface to

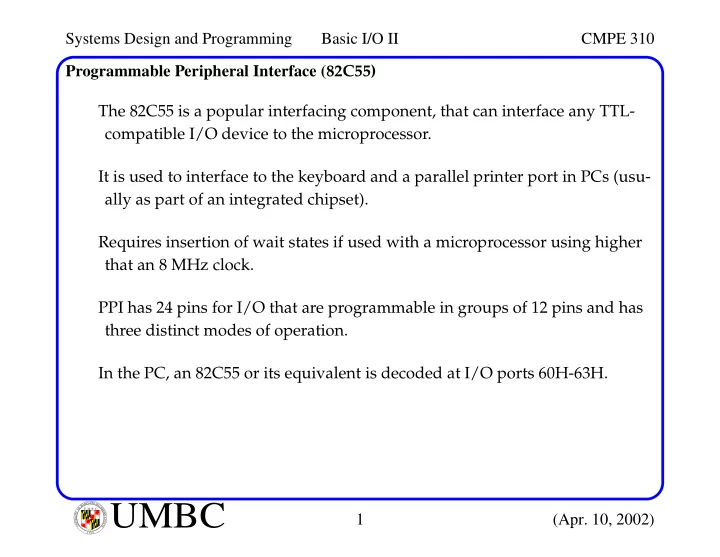

Systems Design and Programming Basic I/O II CMPE 310 Programmable Peripheral Interface ( 82C55) The 82C55 is a popular interfacing component, that can interface any TTL- compatible I/O device to the microprocessor. It is used to interface to the keyboard and a parallel printer port in PCs (usu- ally as part of an integrated chipset). Requires insertion of wait states if used with a microprocessor using higher that an 8 MHz clock. PPI has 24 pins for I/O that are programmable in groups of 12 pins and has three distinct modes of operation. In the PC, an 82C55 or its equivalent is decoded at I/O ports 60H-63H. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 Pinout of 82C55 PPI 82C55 D0 PA0 Group A D1 PA1 D2 PA2 Port A (PA7-PA0) and upper PA3 D3 half of port C (PC7 - PC4) D4 PA4 D5 PA5 D6 PA6 Group B D7 PA7 Port B (PB7-PB0) and lower PB0 PB1 half of port C (PC3 - PC0) PB2 RD PB3 WR PB4 PB5 A0 PB6 I/O Port Assignments A1 PB7 RESET PC0 A 1 A 0 Function CS PC1 Port A PC2 0 0 PC3 Port B 0 1 PC4 Port C 0 1 PC5 VCC PC6 1 Command Register 1 GND PC7 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 Interfacing the 82C55 PPI (Port addresses) 8 PA0 D 7 --D 0 D0 PA1 D1 PA2 D2 PA3 Port A D3 PA4 (C0H) D4 PA5 D5 PA6 D6 PA7 D7 PB0 PB1 82C55 PB2 PB3 Port B IORC RD PB4 (C2H) IOWC WR PB5 A1 A0 PB6 A2 A1 PB7 RESET RESET PC0 CS PC1 A7 A 74ALS138 PC2 Port C 0 B PC3 A3 1 (C4H) PC4 A4 C 2 PC5 VCC 3 PC6 4 GND A6 G1 5 PC7 Command A5 G2A 6 Register 7 A0 G2B (C6H) L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 Programming the 82C55 (Programs ports A, B, C) Command Byte A 7 6 5 4 3 2 1 0 1 Group A Group B Port C (PC7 - PC4) Port C (PC3 - PC0) 1 = input 1 = input 0 output 0 = output Port A Port B 1 = input 1 = input 0 = output 0 = output Mode Mode 0 = mode 0 00 = mode 0 1 = mode 1 01 = mode 1 1x = mode2 (Sets or resets any bits in port C) Command Byte B 7 6 5 4 3 2 1 0 x x x 0 Bit set/reset 1 = set 0 = reset Selects a bit L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 0 Operation 8-Digit Seven Segment LED Display Interface 82C55 D 7 --D 0 8 A 0 D 0 7 A 7 NC B 0 D 7 IORC RD Gnd IOWC WR A 0 A 0 B 7 A 1 A 1 C 0 Reset Reset CS A 2 I 1 Vcc A 3 O 1 A 4 C 7 A 5 A 6 IO/M A 7 A 15 A 8 A 14 7 A 9 A 13 A 10 O 8 A 12 I 10 A 11 16L8 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 0 Operation Mode 0 operation causes the 82C55 to function as a buffered input device or as a latched output device. In previous example, both ports A and B are programmed as (mode 0) simple latched output ports. Port A provides the segment data inputs to display and port B provides a means of selecting one display position at a time. Different values are displayed in each digit via fast time multiplexing. The values for the resistors and the type of transistors used are determined using the current requirements (see text for details). Textbook has the assembly code fragment demonstrating its use. Examples of connecting LCD displays and stepper motors are also given. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 0 Operation Vcc 4x4 keyboard matrix interface 8 82C55 D 7 -- D 0 A 0 D 0 Row 0 A 7 D 7 B 0 IORC RD Row 1 IOWC WR A 0 A 1 B 7 Row 2 Reset C 0 CS Row 3 A 4 C 7 A 5 Col 0 A 6 Col 1 Col 2 Col 3 A 7 IO/M A 8 16L8 A 15 A 9 A 14 A 10 A 13 A 12 A 11 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 0 Operation Flow chart of a keyboard-scanning procedure Calculate KEY Return key code Scan Keys If key open Check Keys Time Delay for de-bounce Momentary Scan Keys Scan Keys glitch? Time Delay for de-bounce Check Keys If key closed Scan Keys Wait for Release Wait for Keystroke L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 1 Strobed Input Port A and/or port B function as latching input devices. External data is stored in the ports until the microprocessor is ready. Port C used for control or handshaking signals (cannot be used for data). Signal definitions for Mode 1 Strobed Input The strobe input loads data into the port latch on a 0-to-1 transition STB Input buffer full is an output indicating that the input latch IFB contain information Interrupt request is an output that requests an interrupt INTR The interrupt enable signal is neither an input nor an output; it is an INTE internal bit programmed via the PC4(port A) or PC2(port B) bits. PC7,PC6 The port C pins 7 and 6 are general-purpose I/O pins that are available for any purpose. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 1 Strobed Input Mode 1 Port A Timing Diagram PORT A INTE STB PC4 STB A IBF PC5 (Buffer full) IBF INTR PC3 PC6+7 I/O (Interrupt request) INTR Mode 1 Port B RD PORT B INTE PC2 STB B Port IBF PC1 Data read by Data strobed INTR PC0 microprocessor into port L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 1 Strobed Input Example PA 0 D 0 ASCII PA 7 D 7 Keyboard 82C55 STB PC 4 DAV Keyboard encoder debounces the key-switches, and provides a strobe when- ever a key is depressed. DAV is activated on a key press strobing the ASCII-coded key code into Port A. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 1 Strobed Output Similar to Mode 0 output operation, except that handshaking signals are pro- vided using port C. Signal Definitions for Mode 1 Strobed Output Output buffer full is an output that goes low when data is latched OBF in either port A or port B. Goes low on ACK. The acknowledge signal causes the OBF pin to return to 0. ACK This is a response from an external device. Interrupt request is an output that requests an interrupt INTR The interrupt enable signal is neither an input nor an output; it is an INTE internal bit programmed via the PC6(port A) or PC2(port B) bits. PC5,PC4 The port C pins 5 and 4 are general-purpose I/O pins that are available for any purpose. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 1 Strobed Output Mode 1 Port A Timing Diagram PORT A INTE WR PC6 ACK A PC7 OBF OBF (Buffer full) INTR (Interrupt INTR PC3 request) PC4+5 I/O Mode 1 Port B ACK PORT B INTE Port PC2 ACK B PC1 OBF Data sent Data removed from port to port INTR PC0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 13 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Systems Design and Programming Basic I/O II CMPE 310 82C55: Mode 2 Bi-directional Operation Only allowed with port A. Bi-directional bused data used for interfacing two computers, GPIB interface etc. Interrupt request is an output that requests an interrupt INTR Output buffer full is an output indicating that the output buffer OBF contains data for the bi-directional bus Acknowledge is an input that enables tri-state buffers which are ACK otherwise in their high-impedance state STB The strobe input loads data into the port A latch Input buffer full is an output indicating that the input latch IFB contains information for the external bi-directional bus Interrupt enable are internal bits that enable the INTR pin. INTE Bit PC6(INTE1) and PC4(INTE2) PC2,PC1 Theses port C pins are general-purpose I/O pins that are available for any purpose. and PC0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 14 (Apr. 10, 2002) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.