Advanced VLSI Design Subsystem Design CMSC 491C/691C 1 (November 26, 2000 9:39 pm)

UMBC

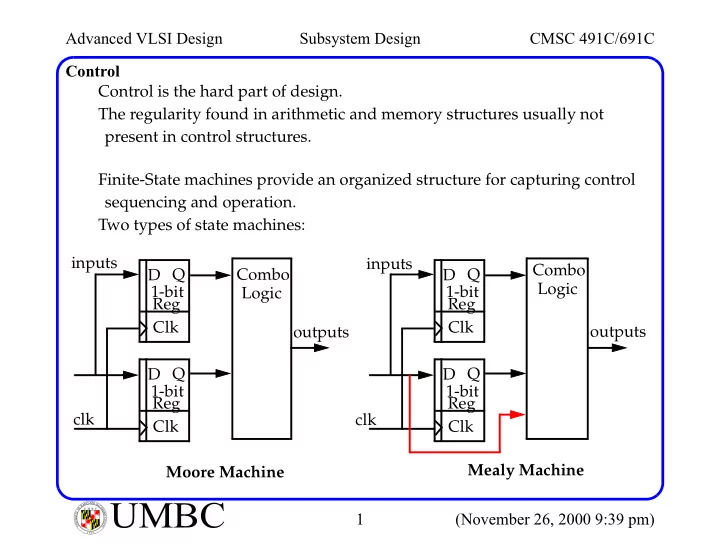

U M B C U N I V E R S I T Y O F M A R Y L A N D B A L T I M O R E C O U N T Y 1 9 6 6Control Control is the hard part of design. The regularity found in arithmetic and memory structures usually not present in control structures. Finite-State machines provide an organized structure for capturing control sequencing and operation. Two types of state machines: Combo inputs

- utputs

D Q 1-bit Reg Clk D Q 1-bit Reg Clk clk Logic Moore Machine Combo inputs

- utputs

D Q 1-bit Reg Clk D Q 1-bit Reg Clk clk Logic Mealy Machine