1

26/10/2001 Reconfigurable Systems 1

ÿþýüûúùø÷öõôóþòñðïîþíï

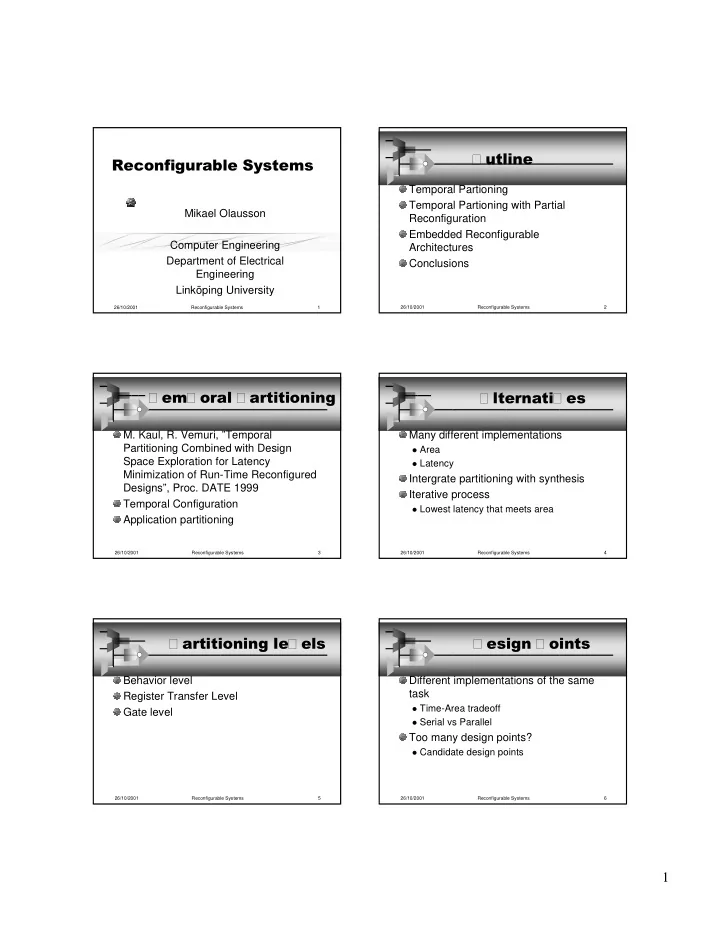

Mikael Olausson Computer Engineering Department of Electrical Engineering Linköping University

26/10/2001 Reconfigurable Systems 2

÷îóùûþ

Temporal Partioning Temporal Partioning with Partial Reconfiguration Embedded Reconfigurable Architectures Conclusions

26/10/2001 Reconfigurable Systems 3

þíüöõóòõöîùîùüûùûø

- M. Kaul, R. Vemuri, ”Temporal

Partitioning Combined with Design Space Exploration for Latency Minimization of Run-Time Reconfigured Designs”, Proc. DATE 1999 Temporal Configuration Application partitioning

26/10/2001 Reconfigurable Systems 4

óîþöûõîùþï

Many different implementations

ÿ Area ÿ Latency

Intergrate partitioning with synthesis Iterative process

ÿ Lowest latency that meets area

26/10/2001 Reconfigurable Systems 5

õöîùîùüûùûøòóþþóï

Behavior level Register Transfer Level Gate level

26/10/2001 Reconfigurable Systems 6

þïùøûòüùûîï

Different implementations of the same task

ÿ Time-Area tradeoff ÿ Serial vs Parallel

Too many design points?

ÿ Candidate design points