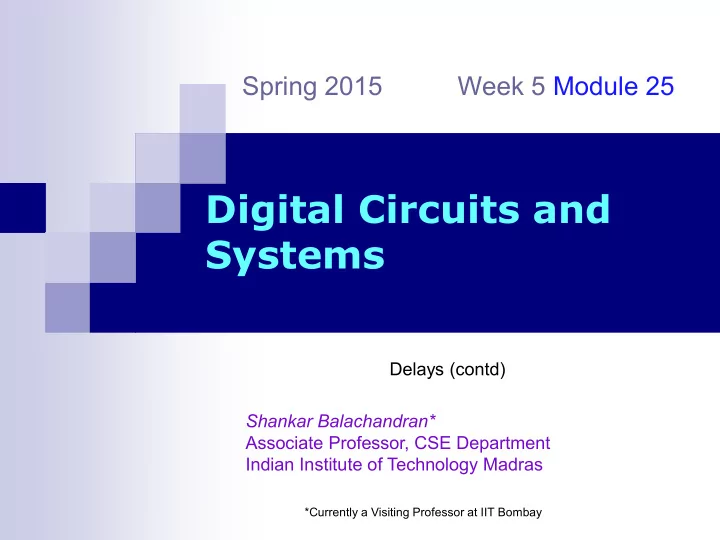

Systems Delays (contd) Shankar Balachandran* Associate Professor, - PowerPoint PPT Presentation

Spring 2015 Week 5 Module 25 Digital Circuits and Systems Delays (contd) Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay Sequential Element Delays

Spring 2015 Week 5 Module 25 Digital Circuits and Systems Delays (contd) Shankar Balachandran* Associate Professor, CSE Department Indian Institute of Technology Madras *Currently a Visiting Professor at IIT Bombay

Sequential Element Delays More complicated than combinational logic elements Two components Setup and Hold time Intrinsic propagation delays Delays 2

Setup and Hold Times Setup time , t su , is the time period prior to the clock becoming active (edge or level) during which the flip-flop inputs must remain stable. Hold time , t h , is the time after the clock becomes inactive during which the flip-flop inputs must remain stable. Setup time and hold time define a window of time during which the flip-flop inputs cannot change – quiescent interval. Delays 3

Propagation Delay Propagation delay, t pHL and t pLH , has the same meaning as in combinational circuit – beware propagation delays usually will not be equal for all input to output pairs. There can be two propagation delays: t C- Q ( clock →Q delay) and t D-Q ( data →Q delay). For a level or pulse triggered latch: Data input should remain stable till the clock becomes inactive. Clock should remain active till the input change is propagated to Q output. That is, active period of the clock, t w > max { t pLH , t pHL } Delays 4

Latch & Flip-flop Timing Parameters Delays 5

Latch and Flip-flop Timings CLK D t h t C-Q t su Q Flip-flop t h t su t h t su Q Latch t C-Q t C-Q t D-Q Delays 6

More Precise FF Setup and Hold Times CLK t D t Q t 350 300 Minimum Data-Output Clk-Output [ps] 250 200 150 Setup Hold 100 Sampling Window 50 0 -200 -150 -100 -50 0 50 100 150 200 Data-Clk [ps] Delays 7

Characterizing Timing • Setup time, hold time • Propagation delays t D-Q t D-C t D-C t C-Q t C-Q Latch Flip-Flop Delays 8

End of Week 5: Module 25 Thank You Delays 9

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.