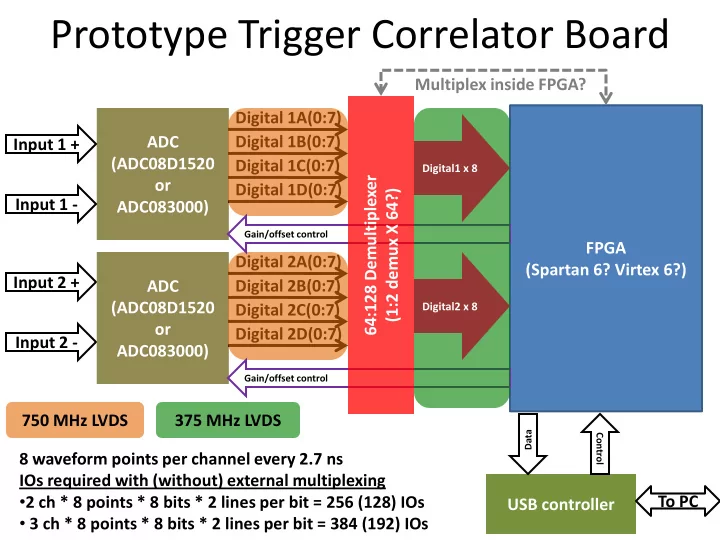

ADC (ADC08D1520

- r

ADC083000) Input 1 + Input 1 - Input 2 + Input 2 - ADC (ADC08D1520

- r

ADC083000) FPGA (Spartan 6? Virtex 6?) USB controller

Prototype Trigger Correlator Board

Control Data

To PC Digital 1A(0:7) Digital 1B(0:7) Digital 1C(0:7) Digital 1D(0:7) Digital 2A(0:7) Digital 2B(0:7) Digital 2C(0:7) Digital 2D(0:7) 750 MHz LVDS

Gain/offset control Gain/offset control

64:128 Demultiplexer (1:2 demux X 64?) 375 MHz LVDS 8 waveform points per channel every 2.7 ns IOs required with (without) external multiplexing

- 2 ch * 8 points * 8 bits * 2 lines per bit = 256 (128) IOs

- 3 ch * 8 points * 8 bits * 2 lines per bit = 384 (192) IOs

Digital1 x 8 Digital2 x 8

Multiplex inside FPGA?