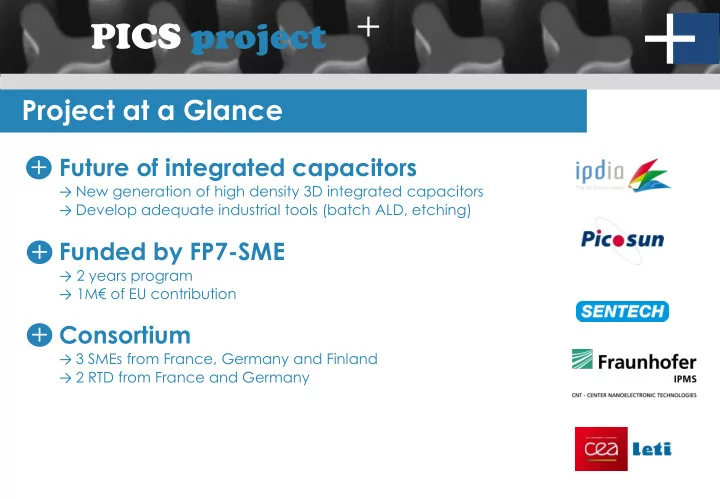

PICS project

Project at a Glance

Future of integrated capacitors

→ New generation of high density 3D integrated capacitors → Develop adequate industrial tools (batch ALD, etching)

Funded by FP7-SME

→ 2 years program → 1M€ of EU contribution

Consortium

→ 3 SMEs from France, Germany and Finland → 2 RTD from France and Germany