1

Overview of Computer Organization

Chapter 1

- S. Dandamudi

2003

To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer-Verlag, 2003.

S. Dandamudi Chapter 1: Page 2

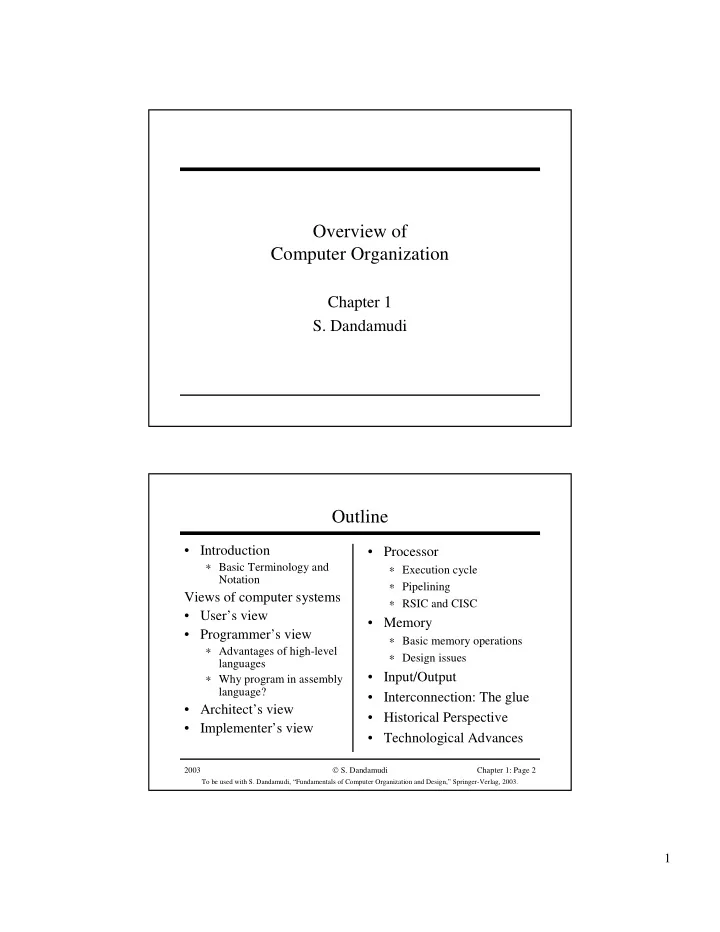

Outline

- Introduction

∗ Basic Terminology and Notation

Views of computer systems

- User’s view

- Programmer’s view

∗ Advantages of high-level languages ∗ Why program in assembly language?

- Architect’s view

- Implementer’s view

- Processor

∗ Execution cycle ∗ Pipelining ∗ RSIC and CISC

- Memory

∗ Basic memory operations ∗ Design issues

- Input/Output

- Interconnection: The glue

- Historical Perspective

- Technological Advances