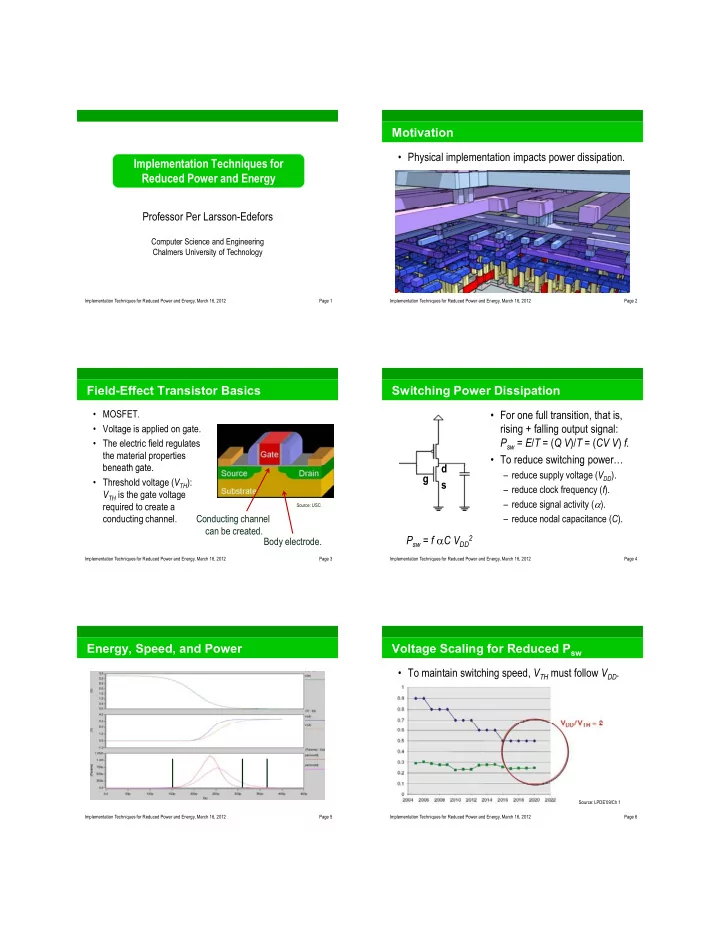

Implementation Techniques for Reduced Power and Energy

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 1

Computer Science and Engineering Chalmers University of Technology

Professor Per Larsson-Edefors

- Physical implementation impacts power dissipation.

Motivation

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 2

- MOSFET.

- Voltage is applied on gate.

- The electric field regulates

the material properties beneath gate

Field-Effect Transistor Basics

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 3

beneath gate.

- Threshold voltage (VTH):

VTH is the gate voltage required to create a conducting channel.

Source: USC

Conducting channel can be created. Body electrode.

- For one full transition, that is,

rising + falling output signal: Psw = E/T = (Q V)/T = (CV V) f.

- To reduce switching power…

Switching Power Dissipation

d

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 4

g

– reduce supply voltage (VDD). – reduce clock frequency (f). – reduce signal activity (α). – reduce nodal capacitance (C).

Psw = f αC VDD

2

g s d

Energy, Speed, and Power

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 5

- To maintain switching speed, VTH must follow VDD.

Voltage Scaling for Reduced Psw

Implementation Techniques for Reduced Power and Energy, March 16, 2012 Page 6 Source: LPDE’09/Ch 1