1

MIPS Assembly Language

Chapter 15

- S. Dandamudi

2003

To be used with S. Dandamudi, “Fundamentals of Computer Organization and Design,” Springer, 2003.

S. Dandamudi Chapter 15: Page 2

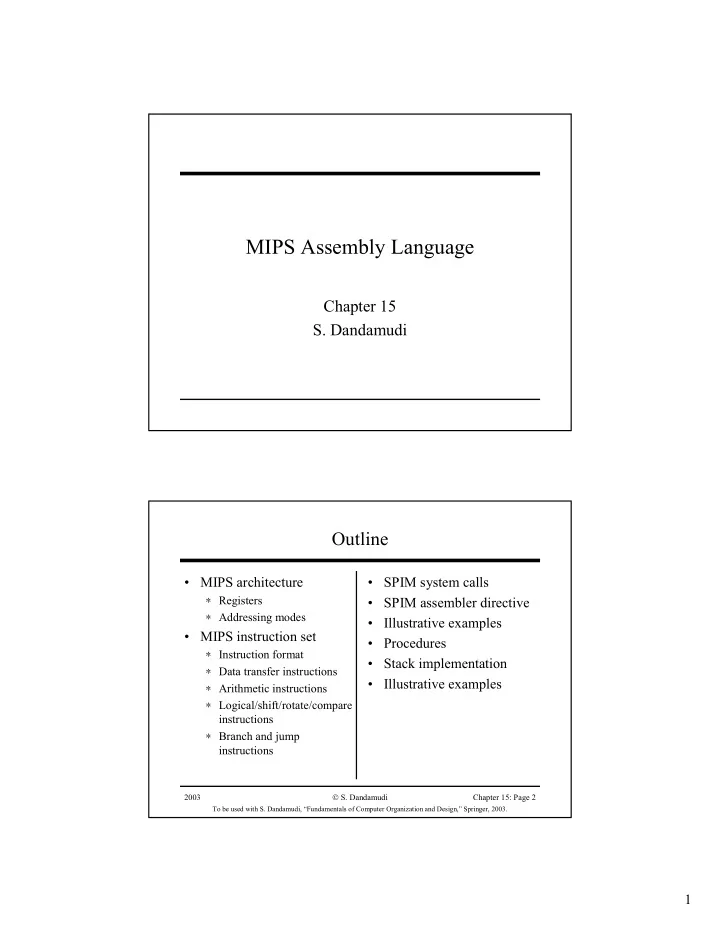

Outline

- MIPS architecture

∗ Registers ∗ Addressing modes

- MIPS instruction set

∗ Instruction format ∗ Data transfer instructions ∗ Arithmetic instructions ∗ Logical/shift/rotate/compare instructions ∗ Branch and jump instructions

- SPIM system calls

- SPIM assembler directive

- Illustrative examples

- Procedures

- Stack implementation

- Illustrative examples