Digital IC-konstruktion

Memories Memories

Viktor Öwall

- Dept. of Electrical and Information Technology

p gy Lund University

Parts of this material was adapted from the instructor material to

Viktor Öwall, ASIC/DSP, CCCD, Dept. of Applied Electronics, Lund University, Sweden-www.tde.lth.se/home/vikt-vikt@tde.lth.se

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Parts of this material was adapted from the instructor material to Jan M. Rabaey, Digital Integrated Circuits: A Design Perspective

Digital IC-konstruktion

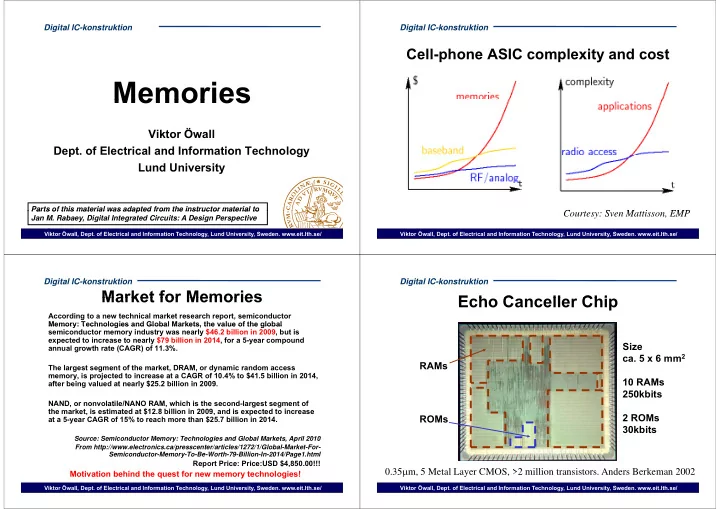

Cell-phone ASIC complexity and cost

C t S M tti EMP

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Courtesy: Sven Mattisson, EMP

Digital IC-konstruktion

Market for Memories Market for Memories

According to a new technical market research report, semiconductor Memory: Technologies and Global Markets, the value of the global Memory: Technologies and Global Markets, the value of the global semiconductor memory industry was nearly $46.2 billion in 2009, but is expected to increase to nearly $79 billion in 2014, for a 5-year compound annual growth rate (CAGR) of 11.3%. The largest segment of the market, DRAM, or dynamic random access memory, is projected to increase at a CAGR of 10.4% to $41.5 billion in 2014, ft b i l d t l $25 2 billi i 2009 after being valued at nearly $25.2 billion in 2009. NAND, or nonvolatile/NANO RAM, which is the second-largest segment of th k t i ti t d t $12 8 billi i 2009 d i t d t i the market, is estimated at $12.8 billion in 2009, and is expected to increase at a 5-year CAGR of 15% to reach more than $25.7 billion in 2014.

So rce Semicond ctor Memor Technologies and Global Markets April 2010 Source: Semiconductor Memory: Technologies and Global Markets, April 2010 From http://www.electronics.ca/presscenter/articles/1272/1/Global-Market-For- Semiconductor-Memory-To-Be-Worth-79-Billion-In-2014/Page1.html

Report Price: Price:USD $4 850 00!!!

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

Report Price: Price:USD $4,850.00!!!

Motivation behind the quest for new memory technologies! Digital IC-konstruktion

E h C ll Chi Echo Canceller Chip

Size RAMs

- ca. 5 x 6 mm2

10 RAMs 10 RAMs 250kbits ROMs 2 ROMs 30kbits

Viktor Öwall, Dept. of Electrical and Information Technology, Lund University, Sweden. www.eit.lth.se/

0.35m, 5 Metal Layer CMOS, >2 million transistors. Anders Berkeman 2002