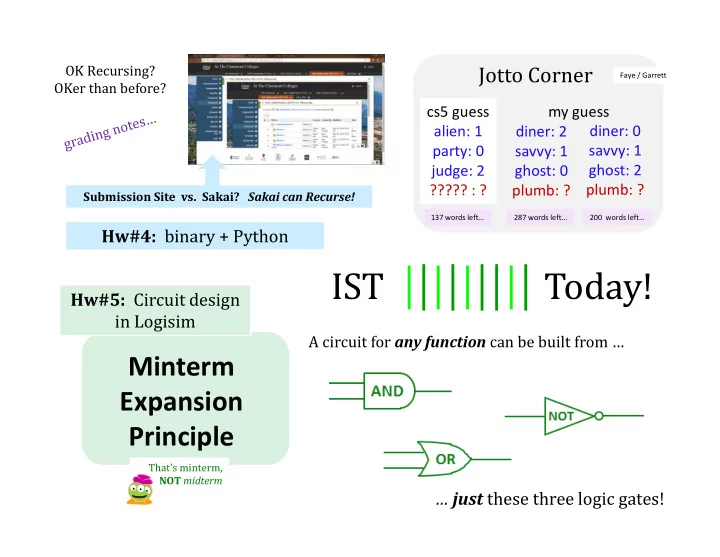

IST Today!

Minterm Expansion Principle

That's minterm, NOT midterm

Hw#5: Circuit design in Logisim

OK Recursing? OKer than before?

A circuit for any function can be built from …

… just these three logic gates!

Submission Site vs. Sakai? Sakai can Recurse!

Jotto Corner

cs5 guess alien: 1 party: 0 judge: 2 ????? : ? my guess diner: 2 savvy: 1 ghost: 0 plumb: ?

Faye / Garrett

diner: 0 savvy: 1 ghost: 2 plumb: ?

200 words left… 287 words left… 137 words left…

Hw#4: binary + Python