A

Digitaltechnik

4 Arithmetik

Revision 1.1

Diskretisierung Einfache Addierer Carry-Select-Addierer Conditional-Sum-Addierer Conditional-Sum-Addierer Carry-Look-Ahead Addierer Multiplizierer Diskretisierung

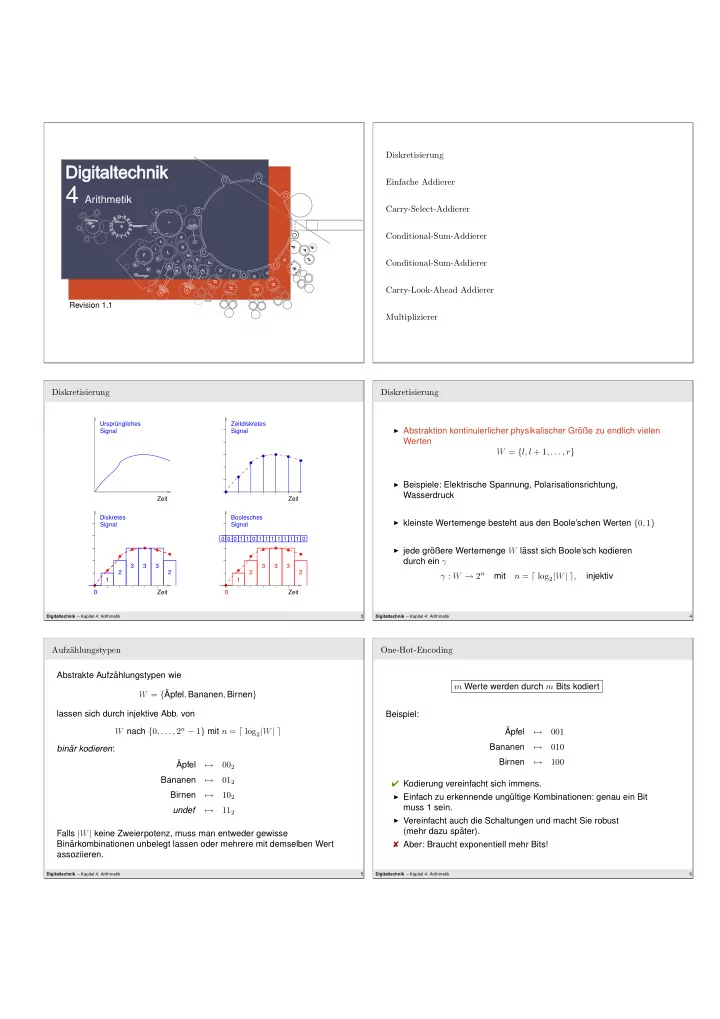

0 1 1 0 1 1 1 1 1 1 1 0 1 2 3 3 3 2 1 2 3 3 3 2 Zeit Zeit Zeit Zeit Boolesches Signal Zeitdiskretes Signal Diskretes Signal Urspr¨ ungliches Signal

Digitaltechnik – Kapitel 4: Arithmetik 3

Diskretisierung

◮ Abstraktion kontinuierlicher physikalischer Gr¨

- ße zu endlich vielen

Werten W = {l, l + 1, . . . , r}

◮ Beispiele: Elektrische Spannung, Polarisationsrichtung,

Wasserdruck

◮ kleinste Wertemenge besteht aus den Boole’schen Werten {0, 1} ◮ jede gr¨

- ßere Wertemenge W l¨

asst sich Boole’sch kodieren durch ein γ γ : W → 2n mit n = ⌈ log2|W| ⌉, injektiv

Digitaltechnik – Kapitel 4: Arithmetik 4

Aufz¨ ahlungstypen Abstrakte Aufz¨ ahlungstypen wie W = { ¨ Apfel, Bananen, Birnen} lassen sich durch injektive Abb. von W nach {0, . . . , 2n − 1} mit n = ⌈ log2|W| ⌉ bin¨ ar kodieren: ¨ Apfel → 002 Bananen → 012 Birnen → 102 undef → 112 Falls |W| keine Zweierpotenz, muss man entweder gewisse Bin¨ arkombinationen unbelegt lassen oder mehrere mit demselben Wert assoziieren.

Digitaltechnik – Kapitel 4: Arithmetik 5

One-Hot-Encoding m Werte werden durch m Bits kodiert Beispiel: ¨ Apfel → 001 Bananen → 010 Birnen → 100 ✔ Kodierung vereinfacht sich immens.

◮ Einfach zu erkennende ung¨

ultige Kombinationen: genau ein Bit muss 1 sein.

◮ Vereinfacht auch die Schaltungen und macht Sie robust

(mehr dazu sp¨ ater). ✘ Aber: Braucht exponentiell mehr Bits!

Digitaltechnik – Kapitel 4: Arithmetik 6