Field Programmable Gate Array - What is it? 2D array of logic blocks - - PowerPoint PPT Presentation

Field Programmable Gate Array - What is it? 2D array of logic blocks - - PowerPoint PPT Presentation

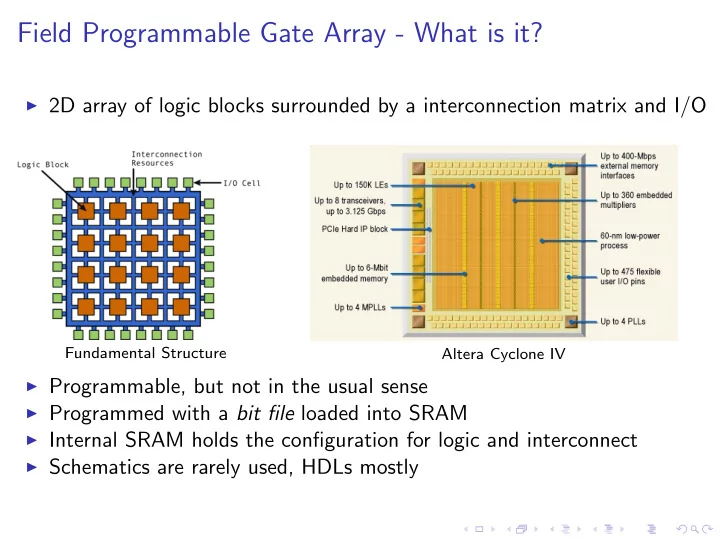

Field Programmable Gate Array - What is it? 2D array of logic blocks surrounded by a interconnection matrix and I/O Fundamental Structure Altera Cyclone IV Programmable, but not in the usual sense Programmed with a bit file loaded into

FPGAs as compared to ASICs - Usage models

◮ ASIC

◮ Application Specific - does one thing - fixed circuit ◮ MPEG Decoder, Dolby Noise Reduction, MRI Image Processor ◮ Very cheap in very large volumes

◮ FPGA

◮ Extremely Flexible - can do many things - infinitely changeable ◮ uC, MPEG Decoder, digital signal processor,... ◮ Relatively expensive in even fairly large volumes

FPGAs as compared to ASICs - Architecture

◮ ASIC

◮ About 200 Predesigned (standard) cells: NOR, NAND, XOR ◮ Each cell chosen and sized by synthesis ◮ Very dense, very optimized design ◮ Full mask set needed, diffusion, contacts, wells,...everything ◮ Requires test circuitry insertion, test vector generation

◮ FPGA

◮ Combo logic via Logic Elements (LE) - SRAM memory lookup ◮ Prefabricated PLL, Embedded Memory, Embedded Multipliers ◮ Prefabricated interconnect fabric, clock trees, and I/O cells ◮ Fully tested at manufacture

FPGAs as compared to ASICs - Time and Cost

◮ ASIC

◮ Full mask set 1M$ (90nm) to 2M$ (40nm) dollars ◮ NRE 50-250K$ ◮ Sign-off to 1st article 2-3 months ◮ Re-spin, 2-3 months total, 100’s of K$, loss of market window ◮ Expensive tool-set; Takes a minimum of 1M$ to play the game ◮ 1 seat of DC shell is about 150-200K$

◮ FPGA

◮ Parts are prefabricated, no NRE ◮ Respin in one day or less ◮ Tool-set, couple of K$ at most, many are free ◮ No test insertion or vectors, fully tested at manufacture

FPGA Relative advantages/disadvantages

◮ FPGA Advantages

◮ Time to market (TTM): 1 month ≈ 10% market share ◮ Flexibility: one part reused for many projects ◮ Risk: Bugs are easier to find, simple and fast to fix ◮ Capacity of parts continues to increase quickly

◮ FPGA disadvantages

◮ 40x the area of ASIC ◮ 3-4x the delay of ASIC ◮ 12x the power of ASIC (Kuon and Rose, FPGA 2006)