CS6354: Snooping Cache Coherency 7 October 2016 1 To read more - PowerPoint PPT Presentation

CS6354: Snooping Cache Coherency 7 October 2016 1 To read more This days papers: Goodman, Using cache memory to reduce processor-memory traffic Archibald and Baer, Cache Coherence Models: Evaluation Using a Multiprocessor

CS6354: Snooping Cache Coherency 7 October 2016 1

To read more… This day’s papers: Goodman, “Using cache memory to reduce processor-memory traffic” Archibald and Baer, “Cache Coherence Models: Evaluation Using a Multiprocessor Simulation Model” Supplementary readings: Hennessy and Patterson, section 5.3 1

caching shared memories value When does this change? When does this change? CPU1 writes 101 to 0xA300? 200 0xC500 100 0xA300 172 0x9300 address CPU1 300 0xE500 200 0xC400 100 0xA300 value address MEM1 CPU2 2

caching shared memories value When does this change? When does this change? CPU1 writes 101 to 0xA300? 200 0xC500 100 0xA300 172 0x9300 address CPU1 300 0xE500 200 0xC400 100101 0xA300 value address MEM1 CPU2 2

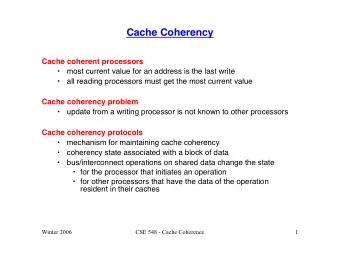

cache coherency states extra information for each cache block overlaps with valid, dirty bits difgerent caches may have difgerent states for same block 3 stored in each cache

scheme 1: MSI read triggered by others writing leaving updates memory required to write Modifjed Shared start Invalid hear write hear read or writeback hear write read or write read write write 4 dashed: overhead on bus; blue: message sent on bus

scheme 1: MSI read triggered by others writing leaving updates memory required to write Modifjed Shared start Invalid hear write hear read or writeback hear write read or write read write write 4 dashed: overhead on bus; blue: message sent on bus

scheme 1: MSI read triggered by others writing leaving updates memory required to write Modifjed Shared start Invalid hear write hear read or writeback hear write read or write read write write 4 dashed: overhead on bus; blue: message sent on bus

scheme 1: MSI read triggered by others writing leaving updates memory required to write Modifjed Shared start Invalid hear write hear read or writeback hear write read or write read write write 4 dashed: overhead on bus; blue: message sent on bus

scheme 1: MSI — blue: transition sends bus signal — — Invalid Shared Modifjed Modifjed to Invalid Shared State Modifjed Shared — — Invalid write read hear write hear read 5

MSI example CPU1 writes 102 to 0xA300 0xC500 200 Shared “CPU1 is writing 0xA3000” CPU1 writes 101 to 0xA300 Cache sees write: invalidate 0xA300 Memory updated* Modifjed state — nothing communicated! 100 Nothing changed yet (writeback) “What is 0xA300?” CPU2 reads 0xA300 Modifjed state — must update for CPU2! “Write 102 into 0xA300” CPU2 reads 0xA300 Written back to memory early (could also become Invalid at CPU1) Shared 0xA300 CPU1 0xC400 CPU2 MEM1 address value state 0xA300 100 Shared 200 Shared Shared 0xE500 300 Shared address value state 0x9300 172 6

MSI example CPU1 writes 102 to 0xA300 0xC500 200 Shared “CPU1 is writing 0xA3000” CPU1 writes 101 to 0xA300 Cache sees write: invalidate 0xA300 Memory updated* Modifjed state — nothing communicated! 100 Nothing changed yet (writeback) “What is 0xA300?” CPU2 reads 0xA300 Modifjed state — must update for CPU2! “Write 102 into 0xA300” CPU2 reads 0xA300 Written back to memory early (could also become Invalid at CPU1) Invalid 0xA300 CPU1 0xC400 CPU2 MEM1 address value state 0xA300 100101 Modifjed 200 Shared Shared 0xE500 300 Shared address value state 0x9300 172 6

MSI example CPU1 writes 102 to 0xA300 0xC500 200 Shared “CPU1 is writing 0xA3000” CPU1 writes 101 to 0xA300 Cache sees write: invalidate 0xA300 Memory updated* Modifjed state — nothing communicated! 100 Nothing changed yet (writeback) “What is 0xA300?” CPU2 reads 0xA300 Modifjed state — must update for CPU2! “Write 102 into 0xA300” CPU2 reads 0xA300 Written back to memory early (could also become Invalid at CPU1) Invalid 0xA300 CPU1 0xC400 CPU2 MEM1 address value state 0xA300 101102 Modifjed 200 Shared Shared 0xE500 300 Shared address value state 0x9300 172 6

MSI example CPU1 writes 102 to 0xA300 0xC500 200 Shared “CPU1 is writing 0xA3000” CPU1 writes 101 to 0xA300 Cache sees write: invalidate 0xA300 Memory updated* Modifjed state — nothing communicated! 100 Nothing changed yet (writeback) “What is 0xA300?” CPU2 reads 0xA300 Modifjed state — must update for CPU2! “Write 102 into 0xA300” CPU2 reads 0xA300 Written back to memory early (could also become Invalid at CPU1) Invalid 0xA300 CPU1 200 CPU2 MEM1 address value state 0xA300 102 0xC400 Shared Shared 0xE500 300 Shared address value state 0x9300 172 6

MSI example CPU1 writes 102 to 0xA300 0xC500 200 Shared “CPU1 is writing 0xA3000” CPU1 writes 101 to 0xA300 Cache sees write: invalidate 0xA300 Memory updated* Modifjed state — nothing communicated! 100 Nothing changed yet (writeback) “What is 0xA300?” CPU2 reads 0xA300 Modifjed state — must update for CPU2! “Write 102 into 0xA300” CPU2 reads 0xA300 Written back to memory early (could also become Invalid at CPU1) Invalid 0xA300 CPU1 0xC400 CPU2 MEM1 address value state 0xA300 102 Shared 200 Shared Shared 0xE500 300 Shared address value state 0x9300 172 6

update memory to write value (enter modifjed state), only need to invalidate others more efficient: shorter bus message 7

on cache replacement/writeback still happens — e.g. want to store something else requires writeback if modifjed (= dirty bit) 8 changes state to invalid

scheme 1: MSI Modifjed value is difgerent than memory and I am the only one who has it Shared Invalid I don’t have the value; I will need to ask for it 9 value is the same as memory

MSI complaints modifying (read then write then write) a value often three messages: initial read from memory invalidate other caches (and maybe write to memory) on initial write fjnal writeback 10

scheme 2: MESI Modifjed value is difgerent than memory and I am the only one who has it Exclusive value is same as memory and I am the only one who has it Shared Invalid I don’t have the value; I will need to ask for it 11 value is the same as memory

scheme 2: MESI Invalid otherwise no one will need to write value to memory change state and return unchanged value if they have a copy caches must respond blue = message sent Modifjed Shared Exclusive start hear read read from memory hear write read or write read write hear read read write write cache from read 12

scheme 2: MESI Invalid otherwise no one will need to write value to memory change state and return unchanged value if they have a copy caches must respond blue = message sent Modifjed Shared Exclusive start hear read read from memory hear write read or write read write hear read read write write cache from read 12

scheme 2: MESI Invalid otherwise no one will need to write value to memory change state and return unchanged value if they have a copy caches must respond blue = message sent Modifjed Shared Exclusive start hear read read from memory hear write read or write read write hear read read write write cache from read 12

read for ownership reading to modify a value soon? read into Exclusive state even if reading from cache invalidate and read second way to enter exclusive state 13

MESI complaints have to update memory to share a modifjed value … read from which cache? 14 even though caches read from other caches

scheme 2: MESI Invalid otherwise no one will need to write value to memory change state and return unchanged value if they have a copy caches must respond blue = message sent Modifjed Shared Exclusive start hear read read from memory hear write read or write read write hear read read write write cache from read 15

scheme 3: MOESI Modifjed value is difgerent than memory and I am the only one who has it Owned value is difgerent than memory and I must update memory Exclusive value is same as memory and I am the only one who has it Shared value is same as memory or cache in Owned state Invalid I don’t have the value 16

scheme 3: MOESI hear write invalidate only due to cache replacement (unlike Modifjed state) writing notifjes other caches send value to caches, but not memory blue = message sent Owned Modifjed Shared Exclusive Invalid read write hear write hear read read write or read read write any hear read write write cache read memory 17

scheme 3: MOESI hear write invalidate only due to cache replacement (unlike Modifjed state) writing notifjes other caches send value to caches, but not memory blue = message sent Owned Modifjed Shared Exclusive Invalid read write hear write hear read read write or read read write any hear read write write cache read memory 17

scheme 3: MOESI hear write invalidate only due to cache replacement (unlike Modifjed state) writing notifjes other caches send value to caches, but not memory blue = message sent Owned Modifjed Shared Exclusive Invalid read write hear write hear read read write or read read write any hear read write write cache read memory 17

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.