1

CALTECH CS137 Winter2006 -- DeHon 1

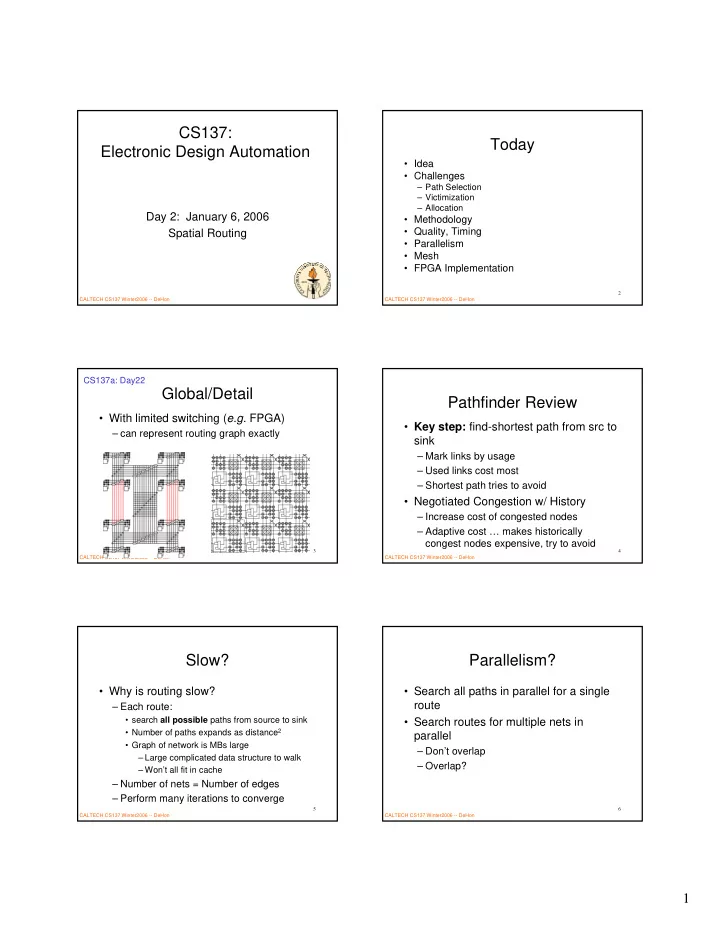

CS137: Electronic Design Automation

Day 2: January 6, 2006 Spatial Routing

CALTECH CS137 Winter2006 -- DeHon 2

Today

- Idea

- Challenges

– Path Selection – Victimization – Allocation

- Methodology

- Quality, Timing

- Parallelism

- Mesh

- FPGA Implementation

CALTECH CS137 Winter2006 -- DeHon 3

Global/Detail

- With limited switching (e.g. FPGA)

– can represent routing graph exactly

CS137a: Day22

CALTECH CS137 Winter2006 -- DeHon 4

Pathfinder Review

- Key step: find-shortest path from src to

sink

– Mark links by usage – Used links cost most – Shortest path tries to avoid

- Negotiated Congestion w/ History

– Increase cost of congested nodes – Adaptive cost … makes historically congest nodes expensive, try to avoid

CALTECH CS137 Winter2006 -- DeHon 5

Slow?

- Why is routing slow?

– Each route:

- search all possible paths from source to sink

- Number of paths expands as distance2

- Graph of network is MBs large

– Large complicated data structure to walk – Won’t all fit in cache

– Number of nets = Number of edges – Perform many iterations to converge

CALTECH CS137 Winter2006 -- DeHon 6

Parallelism?

- Search all paths in parallel for a single

route

- Search routes for multiple nets in