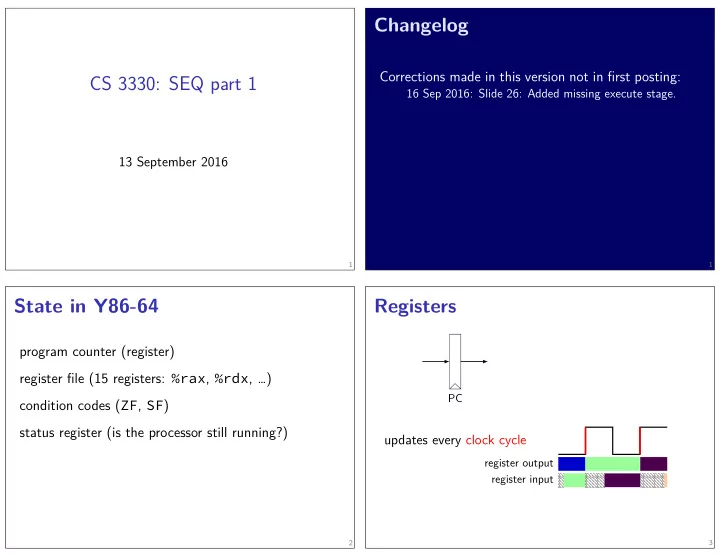

CS 3330: SEQ part 1 condition codes ( ZF , SF ) register input - PowerPoint PPT Presentation

CS 3330: SEQ part 1 condition codes ( ZF , SF ) register input register output updates every clock cycle PC Registers 2 status register (is the processor still running?) register fjle (15 registers: %rax , %rdx , ) 13 September 2016

CS 3330: SEQ part 1 condition codes ( ZF , SF ) register input register output updates every clock cycle PC Registers 2 status register (is the processor still running?) register fjle (15 registers: %rax , %rdx , …) 13 September 2016 program counter (register) State in Y86-64 1 16 Sep 2016: Slide 26: Added missing execute stage. Corrections made in this version not in fjrst posting: Changelog 1 3

State in Y86-64 data output Register fjle 5 value in memory input to write address input time address input %rax, %rdx, … write enable? to write input address data output Mem. register fjle reg values address operation select more? and — andq xor — xorq sub — subq add — addq , addresses Operations needed: B reg #s A A OP B ALU ALUs 6 to write data Data data PC Stat l c i g o l Mem. g Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. o i Mem. g Instr. Memories 4 to PC c i o c l to reg c i g o l 7

Simple ISA 1: addq rbx = 2, 8 byte instructions, no opcode encoding: 8-byte little-endian address jmp label Simple ISA 2: jmp 9 rdx = 6 rax = 1, jmp CPU after cycle 2: PC = 0x02, rdx = 4 rbx = 2, rax = 1, after cycle 1: PC = 0x01, rdx = 3 rbx = 2, 10 PC PC = 0x00, /* 0x08: */ jmp 0x00 after cycle 3: PC = 0x00 after cycle 2: PC = 0x08 after cycle 1: PC = 0x10 PC = 0x00 initially: /* 0x10: */ jmp 0x08 /* 0x00: */ jmp 0x10 Instr. Mem. Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. rax = 1, initially: addq %rXX, %rYY register fjle rXX, rYY Mem. Data ZF/SF reg #s %rax, %rdx, … Mem. add Instr. PC addq CPU 8 no other instructions 1 byte instructions, no opcode encoding: 4-bit register # , 4-bit register # split (contains ALU) /* 0x01: */ addq %rbx, %rdx rbx = 2, /* 0x00: */ addq %rax, %rdx plus one rdx = ?? rbx = ??, rax = ??, after cycle 2: PC = ????, rdx = 4 rax = 1, /* 0x00: */ addq %rax, %rdx after cycle 1: PC = ????, rdx = 3 rbx = 2, rax = 1, PC = 0x00, initially: /* 0x01: */ addq %rbx, %rdx 11

Multiplexers not in listing ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. PC jmp+nop CPU 14 PC Mem. valP valC icode 1 jmp dest 0 nop Dest 0 7 Data split 0 Dest not in listing PC valP valC icode 1 jmp dest 0 nop 0 MUX 7 jmp Dest 0 1 nop + 1 (nop size) dest opcode 0 if nop 1 if jmp jmp Dest 1 MUX 0 1 c 0 1 b 1 0 a 0 output (many bits) d select bit 0 select bit 1 truth table: = a or b or c or d select = 0 or 1 or 2 or 3 output d c b a 1 12 nop ZF/SF + 1 (nop size) dest opcode 0 if nop 1 if jmp MUX split Mem. Data reg #s Simple ISA 3: Jmp or No-Op %rax, %rdx, … register fjle Mem. Instr. PC jmp+nop CPU 13 nop — encoded as 0x10 jmp LABEL — encoded as 0x70 + address actual subset of Y86-64 14

jmp+nop CPU split MUX + immediate opcode convert MUX Mem. +10 Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. +2 rrmovq rA, rB mov-to-register CPU V rmmovq %rXX, 10(%rYY) mrmovq 10(%rXX), %rYY rrmovq %rXX, %rYY irmovq $constant, %rYY Simple ISA 4B: Mov 16 D 0 rA rB 2 5 mrmovq D(rB), rA F rB 0 3 irmovq V, rB 0 rA rB PC 15 PC split + 1 (nop size) dest opcode 0 if nop 1 if jmp MUX Mem. 1 Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. nop 0 mrmovq 10(%rXX), %rYY valC rrmovq %rXX, %rYY irmovq $constant, %rYY Simple ISA 4: Mov-to-register 14 not in listing PC valP icode jmp Dest 1 jmp dest 0 nop Dest 0 7 17

mov CPU ret g o l Mem. Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. PC Stages in Y86-64 19 call function c popq %rax (update %rsp ) popq %rax irmovq $1000, %r8 addq %r9, %r8 call function (saves next PC) mrmovq 1000(%r9), %r8 addq %r8, %r9 to PC c i g o l to reg i l i fetch PC update — compute next value of PC write back — write to register fjle memory — read or write data memory execute — arithmetic (including of addresses) decode — read register fjle fetch — read instruction memory, split instruction Stages 20 PC update back write memory execute decode to PC o c i g o l to reg c i g o l c i g PC c g +10 4 rmmovq rA, D(rB) 0 rA rB 5 mrmovq D(rB), rA F rB 0 3 irmovq V, rB 0 rA rB 2 rrmovq rA, rB from convert opcode write enable +2 o Data Instr. Mem. register fjle %rax, %rdx, … reg #s ZF/SF Mem. MUX split MUX convert opcode immediate + 0 rA rB V D D l c i g o l c i g o l Mem. Data ZF/SF 21 valB valP %rax, %rdx, … register fjle Mem. Instr. valC PC reg #s Connections in Y86-64 18 valM valE valA ← write enable mrmovq 1000(%r9), %r8 pushq %r8 (and %rsp ) rmmovq %r8, 1000(%r9)

Stages and Time PC Mem. Data ZF/SF reg #s %rax, %rdx, … register fjle Mem. Instr. jmp+nop CPU MUX 24 valP valC MUX PC PC update write back memory split 1 if jmp fetch / decode / execute / memory / write back / PC update nop not in listing PC valP valC icode 1 jmp dest 0 Dest 0 if nop 0 7 jmp Dest 0 1 nop + 1 (nop size) dest opcode decode 25 fetch 1; then 3; then 2; then 4 stage Stages Example: nop 22 something else f. 1; then 2; then 3 and 4 at almost the same time e. d. 2. memory changes 1; then 2; then 3; then 4 c. 1; then 2, 3, and 4 at almost the same time b. 1; then 2, 3, and 4 in any order a. 4. PC changes nop decode memory input wire to PC register fetch jmp dest nop stage happen pushq %rax instruction: 1. instruction read Stages Example: nop/jmp 23 3. %rsp changes write back name of a wire from instruction memory part of output wires PC update icode : ifun ← M 1 [ PC ] For the design shown, order when these events valP ← PC + 1 ← means putting a value on a wire ← means putting value on PC ← valP icode : ifun ← M 1 [ PC ] icode : ifun ← M 1 [ PC ] valP ← PC + 1 valC ← M 8 [ PC + 1] PC ← valP PC ← valC

Stages Example: rmmovq/mrmovq opcode from convert opcode write enable +10 +2 MUX + immediate convert 2 MUX split Mem. Data ZF/SF reg #s %rax, %rdx, … register fjle rrmovq rA, rB 0 rA rB Instr. V valM valE valA valB valC valP D D 0 rA rB irmovq V, rB 4 rmmovq rA, D(rB) 0 rA rB 5 mrmovq D(rB), rA F rB 0 3 Mem. PC stage naming output wires of register fjle rmmovq rA, D(rB) mrmovq D(rB), rA fetch decode execute memory write back mov CPU PC update assignment means: 27 but would be harmless setting memory input wires to valA and naming the output of the data memory assignment means: assignment means: setting register fjle input wires to valM 26 assignment means: icode : ifun ← M 1 [ PC ] icode : ifun ← M 1 [ PC ] valP ← PC + 10 valP ← PC + 10 ← write enable valC ← M 8 [ PC + 2] valC ← M 8 [ PC + 2] valA ← R [ rA ] valB ← R [ rB ] valB ← R [ rB ] setting address wires to valE and reading R [ rA ] not needed valE ← valB + valC valE ← valB + valC setting register number input register fjle and M 8 [ valE ] ← valA valM ← M 8 [ valE ] setting register fjle write enable to true R [ rA ] ← valM setting address wires to valE and PC ← valP PC ← valP setting memory write enable to 1

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.

![R = k [ x 1 , . . . , x n ] / I Universal Property of k [ x ] Lemma k [ x ] and x](https://c.sambuz.com/1030446/r-s.webp)