1

Giorgio Buttazzo

g.buttazzo@sssup.it

Scuola Superiore Sant’Anna

2

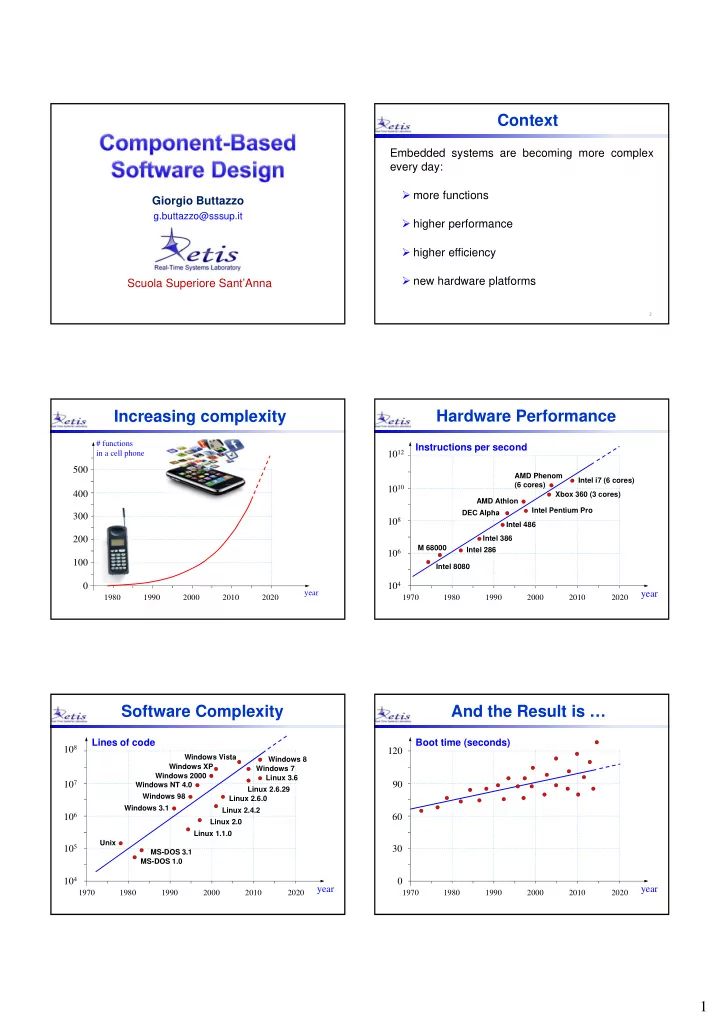

Context

Embedded systems are becoming more complex every day:

- more functions

- higher performance

- higher efficiency

- new hardware platforms

Increasing complexity

1990 2000 2010

100 200

# functions in a cell phone 1980 year 2020

300 400 500

Hardware Performance

1990 2000 2010 1980

year

2020

104 106 108 1010 1012

1970

Instructions per second

Intel 8080 M 68000 Intel 286 Intel 386 Intel 486 Intel Pentium Pro DEC Alpha AMD Athlon Xbox 360 (3 cores) Intel i7 (6 cores) AMD Phenom (6 cores)

Software Complexity

year 104 105 106 107 108 Lines of code

1990 2000 2010 1980 2020 1970

MS-DOS 1.0 Windows 3.1 Windows 2000 Windows XP Windows 7 Windows Vista Unix Windows NT 4.0 Linux 3.6 Linux 2.6.0 Linux 2.4.2 Linux 2.6.29 Windows 98 MS-DOS 3.1 Linux 1.1.0 Linux 2.0 Windows 8