SLIDE 1

CMPE 646: VLSI Design Verification and Test

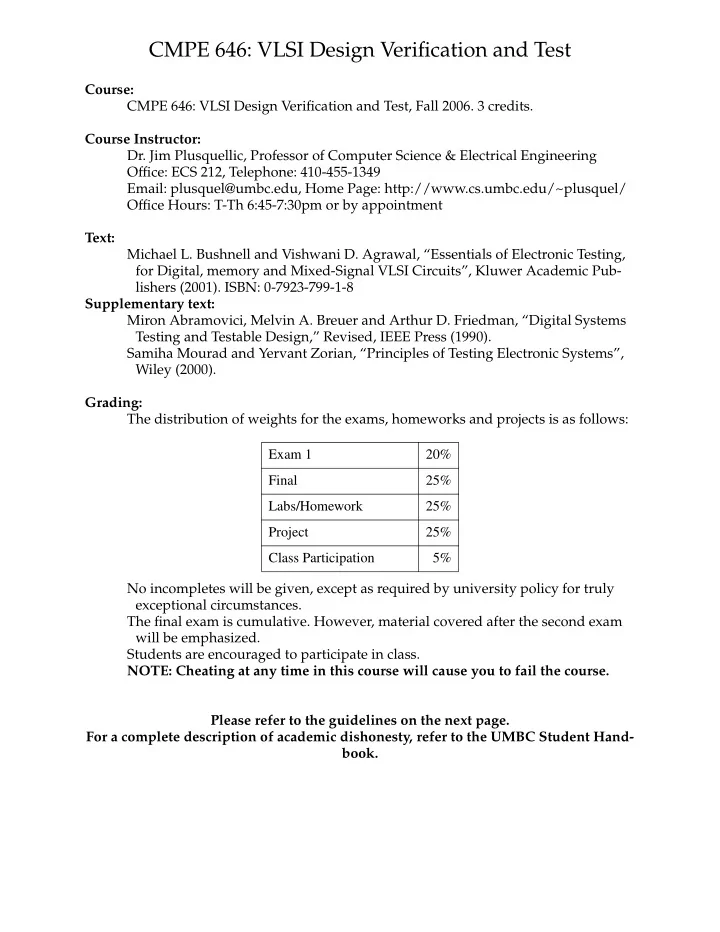

Course: CMPE 646: VLSI Design Verification and Test, Fall 2006. 3 credits. Course Instructor:

- Dr. Jim Plusquellic, Professor of Computer Science & Electrical Engineering