UMBC A B M A L T F O U M B C I M Y O R T 1 (Nov. - PowerPoint PPT Presentation

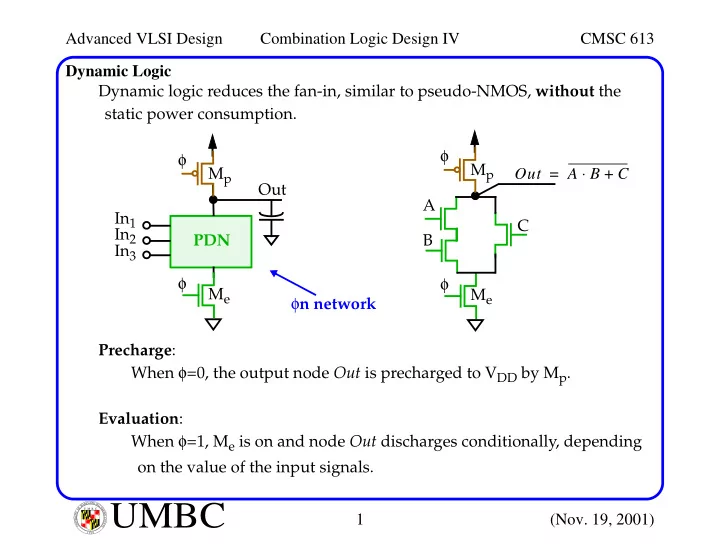

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic Dynamic logic reduces the fan-in, similar to pseudo-NMOS, without the static power consumption. M p Out A B C M p = + Out A In 1 C In 2 B PDN In 3

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic Dynamic logic reduces the fan-in, similar to pseudo-NMOS, without the static power consumption. φ φ ⋅ M p Out A B C M p = + Out A In 1 C In 2 B PDN In 3 φ φ M e M e φ n network Precharge : When φ =0, the output node Out is precharged to V DD by M p . Evaluation : When φ =1, M e is on and node Out discharges conditionally, depending on the value of the input signals. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 1 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic If no path exists during evaluate, then Out remains high via C L (diffusion, wiring and gate capacitance). Note that once Out is discharged, it cannot be recharged. Therefore, the inputs can make at most one transition during evaluation. Properties: • The logic function is implemented in the NMOS pull-down network. • The # of transistors is N+2 instead of 2N • It is non-ratioed (noise margin does not depend on transistor ratios). • It only consumes dynamic power. • Faster switching due to reduced internal and downsteam capacitance. Steady-state behavior : V OL and V OH are GND and V DD . Our standard definitions of noise margins and switching thresholds do not include time , which is required in this case. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 2 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic Steady-state behavior (cont): For example, noise margins depend on the length of the evaluate. If clk is too long, leakage affects the high output level significantly. Since the pull down network starts to conduct when the input signal exceeds V Tn , it is reasonable to set V M , V IH , V IL = V Tn . Therefore, NM L is very low. Note that this is a conservative estimate since subthreshold leakage occurs for inputs below V Tn . Also note that the high output level is sensitive to noise and coupling disturbances because of its high output impedance. The high value of NM H compensates for this increased sensitivity. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 3 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic Dynamic behavior: Also, after precharge, the output is high. Therefore, t pLH = 0! This is somewhat unfair since it ignores the precharge time. The designer is free to choose the size of the PMOS device, smaller is faster but increases load and t pHL . The t pHL is proportional to C L and current-sinking capabilities of PDN. M e slows down the gate a little. Capacitive coupling 6 φ 4 V out (V) Evaluate Precharge 2 0 t (nsec) 0.0 2.0 4.0 6.0 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 4 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic There are three sources of noise: • Charge Leakage φ Via reversed-biased t diffusion diodes and subthreshold leakage Precharge Evaluate t Sets the minimum clock to 250Hz to 1kHz (testing difficulties) • Charge Sharing ∆ V out > V Tn If φ then V out and V x reach the same value. M p Out C a C out A ∆ V out V DD - - - - - - - - - - - - - - - - - - - - = – C a C L M a + X B=0 C a M b Target is to keep ∆ V out < V Tp φ since output M e C b may drive a static gate. C a /C L < 0.2. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 5 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Dynamic Logic One way to combat both of these: bleeder φ φ φ M bl M bl M p M p Out Out A A M a M a B B M b M b φ φ M e M e Static bleeder Precharge Internal nodes Pseudo-static : M bl is a highly resistive (long and narrow) PMOS transistor. Alternatively, precharge internal nodes using a clock driven PMOS. • Clock Feedthrough The clock is coupled to the storage node via C gs and gate-overlap caps. May forward bias the junction and inject electrons into substrate. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 6 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 DOMINO Logic Cascading Dynamic gates φ Evaluate φ φ M p M p Out 2 In In Out 1 Out 1 φ φ M e M e ∆ V Out 2 t Fix is to restrict the inputs to making only a 0->1 transition during eval. Level restorer. φ φ M p M r M p Out 1 Out 2 In 1 In 2 In 4 PDN PDN In 3 φ φ Fanout also M e M e driven by static inverter. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 7 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 DOMINO Logic During evaluation, either the output of the first DOMINO stays at 0 (no delay!) or makes a 0->1 transition. The transition may ripple all the way down the chain. Properties: • Only non-inverting logic can be implemented. • Appropriate for complex, large fan-out circuits such as ALUs or control cir- cuits. • Very high speeds can be achieved, t pHL = 0. In the past, DOMINO was used in the design of a number of high speed ICs. The first 32-bit microprocessor (BellMAC 32) used it. Recently, pure DOMINO circuits are rare, mainly due to the non-inverting logic property. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 8 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 np-CMOS Logic PUN networks replace the static inverters. φ φ M e φ p block M p Also called Out 1 ZIPPER logic In 1 In 4 PUN In 2 PDN Out 2 In 3 φ φ M p M e Conditionally charged φ n block Note that the φ p blocks are driven with the Clk_bar so that the precharge and evaluate periods coincide. np-CMOS logic style is 20% faster than DOMINO, despite the slower PMOS pull-up devices. The DEC alpha-processor (first at 250MHz) used this logic extensively. Disadv: NM L = V Tn and NM H = |V Tp |. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 9 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Power Consumption We’ve already discussed sources of power consumption in CMOS inverter. 2 P dyn C L V DD f 0->1 = We now discuss the effects of switching activity , glitching and direct-path cur- rent. Note that the factor f 0->1 complicates the analysis for complex gates. Factors affecting the switching activity include the statistics of the input sig- nals , the circuit style (dynamic/static), the function , and network topology . These are incorporated by: 2 P dyn C L V DD P 0->1 f = where f is the average event rate, and P 0->1 is the probability an input transi- tion results in a 0->1 power-consuming event. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 10 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Complex Static Gate Power Consumption Consider a 2-input NOR gate, assume the input signals have a uniform distri- bution of high and low values. e.g., the 4 input combinations, AB = 00 , 01 , 10 , 11 , are equally likely. Therefore, the probability the output is low or high is 3/4 and 1/4 , respec- tively. The probability of an energy consuming transition is the probability that the output is initially low, 3/4, times the probability it will become high, 1/4. 3 1 3 ( ) P 1 × P 0->1 P 0 P 1 P 1 - - - - - - = = 1 – = = - - - - - - 4 4 16 3/4 X 1/4 = 3/16 3/4 X 3/4 = 9/16 1/4 X 1/4 = 1/16 0 1 3/16 L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 11 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Advanced VLSI Design Combination Logic Design IV CMSC 613 Complex Static Gate Power Consumption Note that the output probabilities are no longer uniform . This suggests that the input signals are not uniform, since gates are typically cascaded. The probability that the output is 1 (P 1 ) is a function of the input distributions , P A and P B (the probabilities the inputs are 1). ( ) 1 ( ) P 1 P A P B = 1 – – for the NOR gate. The transition probability is then: ( ) P 1 [ ( ) 1 ( ) ] [ ( ) 1 ( ) ] P 0->1 P 1 P A P B P A P B = 1 – = 1 – 1 – – 1 – – 3-D graph shown in text. Derive these expressions for AND, OR and XOR. L A N R Y D UMBC A B M A L T F O U M B C I M Y O R T 12 (Nov. 19, 2001) I E S R C E O V U I N N U T Y 1 6 9 6

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.