Chenyang Lu 1

TinyOS

Chenyang Lu 2

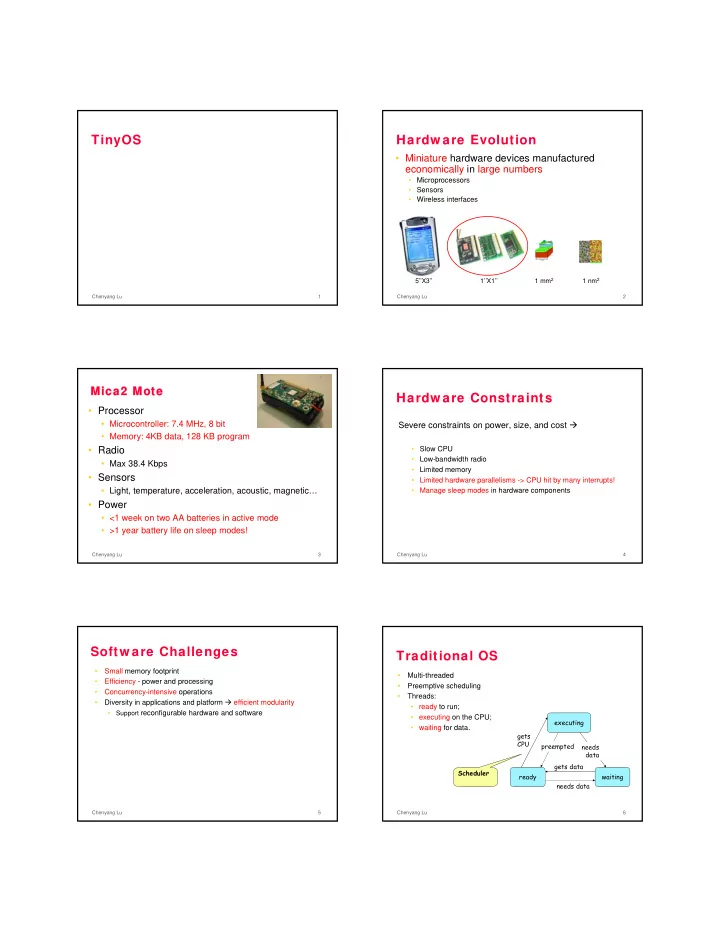

Hardw are Evolution

- Miniature hardware devices manufactured

economically in large numbers

- Microprocessors

- Sensors

- Wireless interfaces

5’’X3’’ 1’’X1’’ 1 mm2 1 nm2

Chenyang Lu 3

Mi Mica2 M ca2 Mote te

- Processor

- Microcontroller: 7.4 MHz, 8 bit

- Memory: 4KB data, 128 KB program

- Radio

- Max 38.4 Kbps

- Sensors

- Light, temperature, acceleration, acoustic, magnetic…

- Power

- <1 week on two AA batteries in active mode

- >1 year battery life on sleep modes!

Chenyang Lu 4

Hardw are Constraints

Severe constraints on power, size, and cost

- Slow CPU

- Low-bandwidth radio

- Limited memory

- Limited hardware parallelisms -> CPU hit by many interrupts!

- Manage sleep modes in hardware components

Chenyang Lu 5

Softw are Challenges

- Small memory footprint

- Efficiency - power and processing

- Concurrency-intensive operations

- Diversity in applications and platform efficient modularity

- Support reconfigurable hardware and software

Chenyang Lu 6

Traditional OS

- Multi-threaded

- Preemptive scheduling

- Threads:

- ready to run;

- executing on the CPU;

- waiting for data.

executing ready waiting needs data gets data needs data preempted gets CPU Scheduler