Department of Electrical and Computer Engineering

Slide 1

Robert Betz: 97

The Logic Circuit CAD Process Introduction

This series of lectures looks at the CAD process using the tool set supplied by Altera. This tool set has its own particular way of implementing the design process, but is representative of tool sets by other vendors.

Design Environment

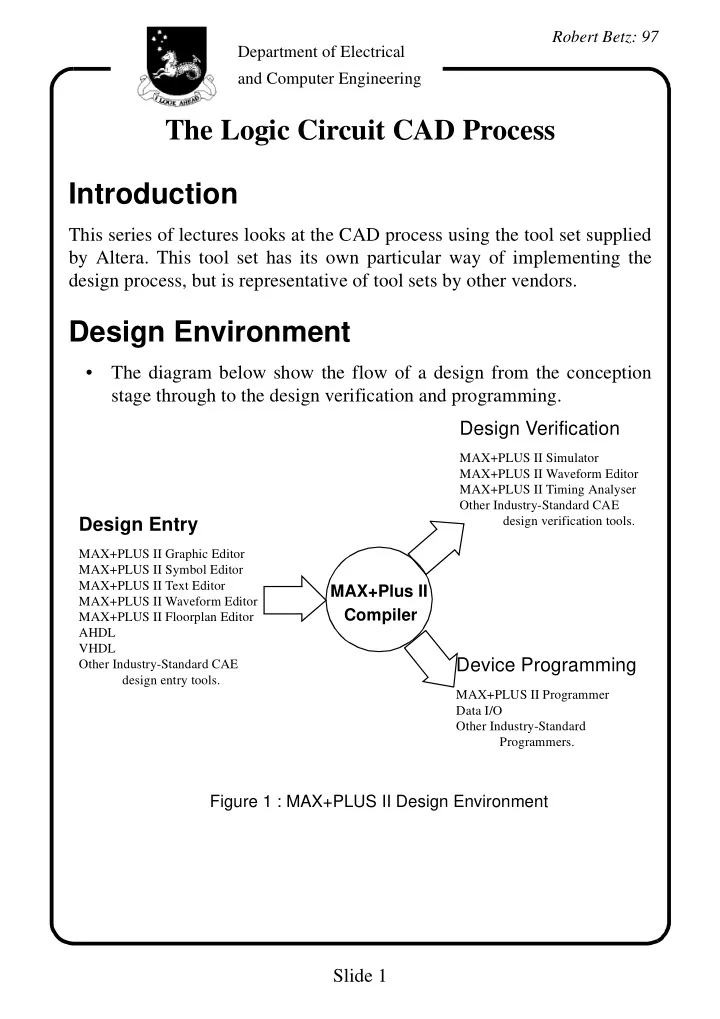

- The diagram below show the flow of a design from the conception

stage through to the design verification and programming.

MAX+Plus II Compiler

Design Entry

MAX+PLUS II Graphic Editor MAX+PLUS II Symbol Editor MAX+PLUS II Text Editor MAX+PLUS II Waveform Editor MAX+PLUS II Floorplan Editor AHDL VHDL Other Industry-Standard CAE design entry tools.

Design Verification

MAX+PLUS II Simulator MAX+PLUS II Waveform Editor MAX+PLUS II Timing Analyser Other Industry-Standard CAE design verification tools.

Device Programming

MAX+PLUS II Programmer Data I/O Other Industry-Standard Programmers.