SLIDE 1

1

Research | Zurich

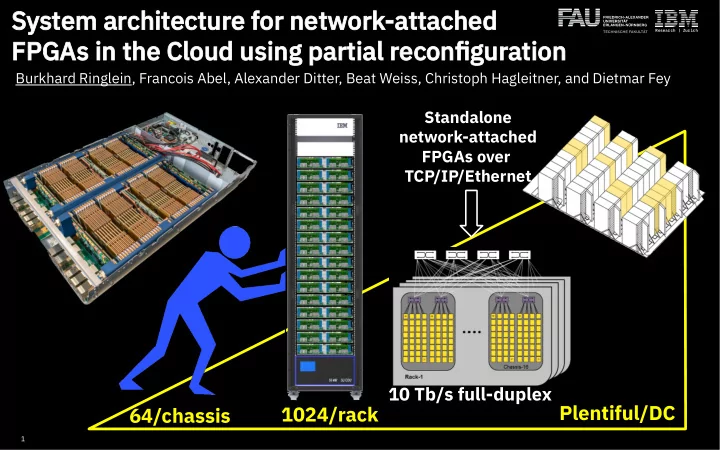

64/chassis 1024/rack

Standalone network-attached FPGAs over TCP/IP/Ethernet

10 Tb/s full-duplex

Plentiful/DC

System a em arch chitect ecture f e for n net etwork-attach ached ed FPGAs i in t the C e Clou

- ud u