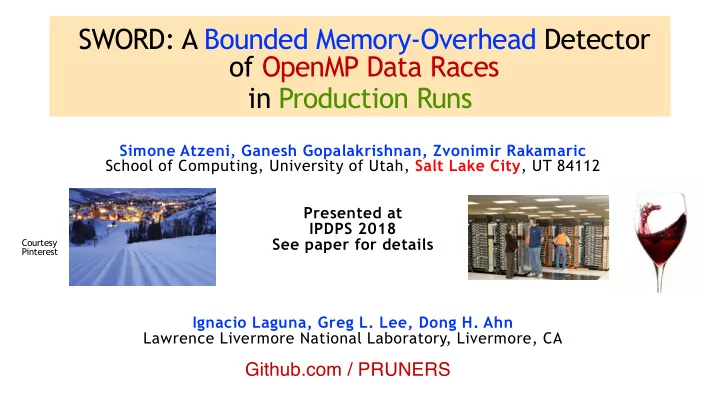

Simone Atzeni, Ganesh Gopalakrishnan, Zvonimir Rakamaric School of Computing, University of Utah, Salt Lake City, UT 84112 Presented at IPDPS 2018 See paper for details Ignacio Laguna, Greg L. Lee, Dong H. Ahn Lawrence Livermore National Laboratory, Livermore, CA

Github.com / PRUNERS

SWORD: A Bounded Memory-Overhead Detector

- f OpenMP Data Races

in Production Runs

Courtesy Pinterest