RD50-MPW3: Slow Control Jos e Mazorra de Cos, Ricardo Marco Hern - PowerPoint PPT Presentation

RD50-MPW3: Slow Control Jos e Mazorra de Cos, Ricardo Marco Hern andez Instituto de F sica Corpuscular (CSIC-UV) RD50 CMOS design Meeting - 3 rd September 2020 Slow Control I 2 C slave and register bank communicated using Wishbone

RD50-MPW3: Slow Control Jos´ e Mazorra de Cos, Ricardo Marco Hern´ andez Instituto de F´ ısica Corpuscular (CSIC-UV) RD50 CMOS design Meeting - 3 rd September 2020

Slow Control I 2 C slave and register bank communicated using Wishbone protocol. Acknowledgment: original design by CERN (EP-ESE-ME) on Verilog translated to VHDL by Herv´ e Chanal (LPC, Clermont-Ferrand). 1 / 5

Communication Logic I 2 C slave composed of three elements state machine for master message interpretation (with watchdog), synchronizer for SDA & SCL and START & STOP detection. gated clock generator for the state machine. Code selectable mutli-byte operation with 7b or 10b addressing. Registers originally designed for multiple bytes per address (pointer +1byte). Reduced to single byte for area reduction and shorter read/write operations, trade-off between available addresses and required resources (area + time). Each 1 ⁄ 2 byte output protected with Hamming(7,4) with extra parity bit single error correction and multiple detection for a factor 2 memory. Triple modular redundancy protection available (formerly applied to I 2 C logic). 2 / 5

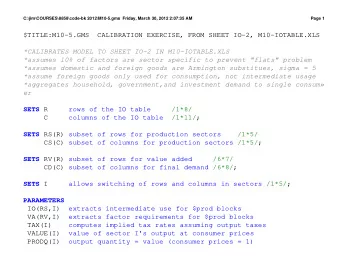

Memory Distribution Address 0x00 left unused. Address Signal Size Default Avoid splitting signal in two regs. 0x01 D VpComp 6b b010011 0x02 D VpTrim 6b b100100 Three sections in register bank: 0x03 D VnSensBias 6b b110010 1) Bias Block Configuration with 0x04 D Vblr 6b b100110 0x05 D Vnsf 6b b101101 one signal(6b) per register. 0x06 D Vnfb Cont 6b b010010 0x07 D Vpfb sw 6b b100110 2) Row Configuration with: 0x08 D VpBias VnCasc 6b b100101 – ENTRIMDAC R (1b, LSB), 0x09 D Vn 6b b010101 – ENINJ R (1b), 0x0A CtrlUnit 6b b000000 – ENCOMPOUTBUFF R (1b), 0x0B ROW0 + ROW1 8b b00000000 – ENSFOUTBUFF R (1b, MSB). 0x0C ROW2 + ROW3 8b b00000000 ... ... ... ... 3) Column Configuration with: 0x1E ROW38 + ROW39 8b b00000000 – TRIMDAC C (4b, LSB), 0x1F COLUMN0 7b b0000000 0x20 COLUMN1 7b b0000000 – ENINJ C (1b), ... ... ... ... – ENCOMPOUTBUFF C (1b), 0x5A COLUMN59 7b b0000000 – ENSFOUTBUFF C (1b, MSB). 3 / 5

Block Boundary Register outputs directly connected to output pins on the block boundary. Additionally, three groups of pins are required: 1) General purpose control signals: – resetB (in): active low asunchronous reset signal for all logic (all regs to 0x00), – clk (in): external clock for all logic (originally 40MHz, last version 320MHz), – ldinit (in): load hard wired initial values (synchronous, active high). 2) I 2 C communication signals: – SCL (in): ”gated” clock provided by the master to manage communication, – SDAi (in): incoming section of the data line separated at GPIO pad, – SDAo (out): outgoing section of the data line separated at GPIO pad, – SDAen (out): signal controlling the direction of the GPIO pad. 3) signals managing the Hamming(7,4) protection coding: – error1 (out): flag indicating a single flip at some register (all OR’d), – errorm (out): flag indicating a single flip at some register (all OR’d), – refresh (in): signal transfering output single flip correction to memory. 4 / 5

Summary & Outlook Working RTL code for a 40x60 pixel matrix available, with testbench. So far multi-byte, 7b addressing and no TMR, but up to discussion. Next, start working on the synthesis to define time constraints. Also, build mixed signal simulation to text GPIO pad (1.8V?). 5 / 5

Thanks a lot for your attention!

Recommend

More recommend

Explore More Topics

Stay informed with curated content and fresh updates.