SLIDE 1

Transactions of the Korean Nuclear Society Virtual Spring Meeting July 9-10, 2020

Radiation Hardened Op-amp Design for 1 Mrad TID

Euntae Choa, Gyuseong Chob, Inyong Kwona

aKorea Atomic Energy Research Institute bKorea Advanced Institute of Science and Technology

entae94@gmail.com, gscho1@kaist.ac.kr, ikwon@kaeri.re.kr

- 1. Introduction

There is increasing demand for radiation hardening electronic circuits that can survive in radiation environments, such as nuclear facilities, space, medical equipment and severe-accident. The vulnerability of electronic circuits in radiation environments is one of the main causes in the development of nuclear electronic

- devices. Therefore, various studies have conducted to

develop radiation hardening electronic devices [1]. This paper especially discuss an operational amplifier (op- amp) among these electronic circuits. Op-amps have been widely used in electronic circuit such as pre-amplifier, integrator and so on. In addition, they are a key component of analog processing systems and an essential part of many signal systems. Recently as the demand increases for integrated circuits, analog circuit designs become more important. For these reasons, we propose a new radiation hardening two-stage op-amp with two ideas, and compare the conventional two-stage op-amp with the proposed two-stage op-amp by simulations.

- 2. Conventional Two-stage Op-amp

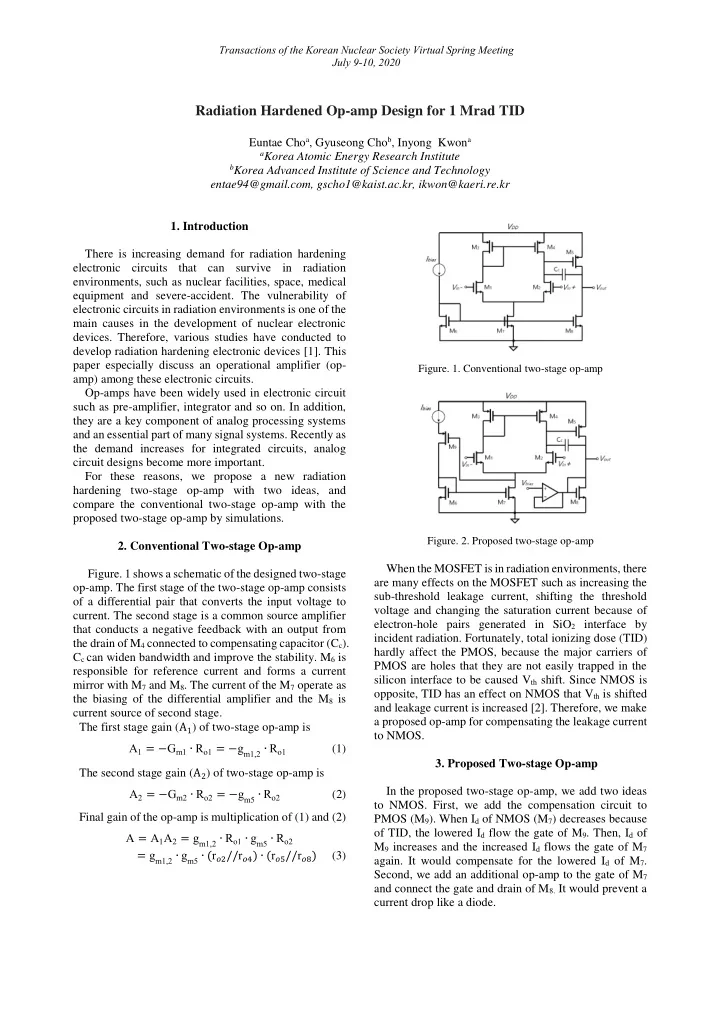

- Figure. 1 shows a schematic of the designed two-stage

- p-amp. The first stage of the two-stage op-amp consists

- f a differential pair that converts the input voltage to

- current. The second stage is a common source amplifier

that conducts a negative feedback with an output from the drain of M4 connected to compensating capacitor (Cc). Cc can widen bandwidth and improve the stability. M6 is responsible for reference current and forms a current mirror with M7 and M8. The current of the M7 operate as the biasing of the differential amplifier and the M8 is current source of second stage. The first stage gain (A1) of two-stage op-amp is A1 = −Gm1 ∙ Ro1 = −gm1,2 ∙ Ro1 (1) The second stage gain (A2) of two-stage op-amp is A2 = −Gm2 ∙ Ro2 = −gm5 ∙ Ro2 (2) Final gain of the op-amp is multiplication of (1) and (2) A = A1A2 = gm1,2 ∙ Ro1 ∙ gm5 ∙ Ro2 = gm1,2 ∙ gm5 ∙ (r𝑝2//r𝑝4) ∙ (r𝑝5//r𝑝8) (3)

- Figure. 1. Conventional two-stage op-amp

- Figure. 2. Proposed two-stage op-amp

When the MOSFET is in radiation environments, there are many effects on the MOSFET such as increasing the sub-threshold leakage current, shifting the threshold voltage and changing the saturation current because of electron-hole pairs generated in SiO2 interface by incident radiation. Fortunately, total ionizing dose (TID) hardly affect the PMOS, because the major carriers of PMOS are holes that they are not easily trapped in the silicon interface to be caused Vth shift. Since NMOS is

- pposite, TID has an effect on NMOS that Vth is shifted

and leakage current is increased [2]. Therefore, we make a proposed op-amp for compensating the leakage current to NMOS.

- 3. Proposed Two-stage Op-amp

In the proposed two-stage op-amp, we add two ideas to NMOS. First, we add the compensation circuit to PMOS (M9). When Id of NMOS (M7) decreases because

- f TID, the lowered Id flow the gate of M9. Then, Id of

M9 increases and the increased Id flows the gate of M7

- again. It would compensate for the lowered Id of M7.