P age 1

CS252/ Culler Lec 18. 1 4/ 2/ 02

CS252 Graduate Computer Architecture

Lecture 18: Branch Prediction + analysis resources => I LP

April 2, 2002 Prof . David E. Culler Comput er Science 252 Spring 2002

CS252/ Culler Lec 18. 2 4/ 2/ 02

Today’s Big I dea

- Reactive: past actions cause system to

adapt use

– do what you did bef ore better – ex: caches – TCP windows – URL completion, . . .

- Proact ive: uses past act ions t o predict

f ut ure act ions

– optimize speculatively, anticipate what you are about to do – branch prediction – long cache blocks – ???

CS252/ Culler Lec 18. 3 4/ 2/ 02

Review: Case f or Branch Prediction when I ssue N instructions per clock cycle

- 1. Branches will arrive up t o n t imes f ast er in

an n- issue processor

- 2. Amdahl’s Law => relat ive impact of t he

control stalls will be larger with the lower pot ent ial CPI in an n- issue processor conversely, need branch predict ion t o ‘see’ potential parallelism

CS252/ Culler Lec 18. 4 4/ 2/ 02

Review: 7 Branch Prediction Schemes

- 1. 1- bit Branch- Predict ion Buf f er

- 2. 2- bit Branch- Predict ion Buf f er

- 3. Correlat ing Branch Predict ion Buf f er

- 4. Tournament Branch Predict or

- 5. Branch Target Buf f er

- 6. I nt egrat ed I nst ruct ion Fet ch Unit s

- 7. Ret urn Address Predict ors

CS252/ Culler Lec 18. 5 4/ 2/ 02

Review: Dynamic Branch Prediction

- Perf ormance = ƒ(accuracy, cost of mispredict ion)

- Branch Hist ory Table: Lower bit s of PC address

index t able of 1- bit values

– Says whether or not branch taken last time – No address check (saves HW, but may not be right branch)

- Problem: in a loop, 1- bit BHT will cause

2 mispredict ions (avg is 9 it erat ions bef ore exit ):

– End of loop case, when it exits instead of looping as bef ore – First time through loop on next time through code, when it predicts exit inst ead of looping – Only 80% accuracy even if loop 90% of the time

CS252/ Culler Lec 18. 6 4/ 2/ 02

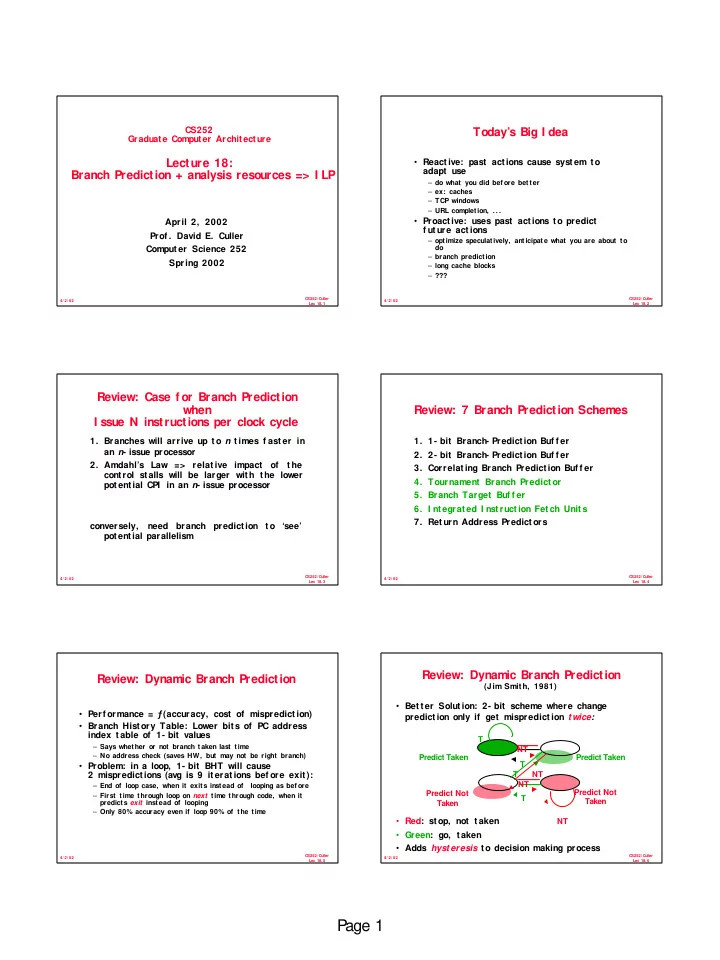

- Bet t er Solut ion: 2- bit scheme where change

predict ion only if get mispredict ion twice:

- Red: st op, not t aken

- Green: go, taken

- Adds hyst eresis t o decision making process

Review: Dynamic Branch Prediction

(Jim Smit h, 1981) T T NT Predict Taken Predict Not Taken Predict Taken Predict Not Taken T NT T NT NT