1

snick snack

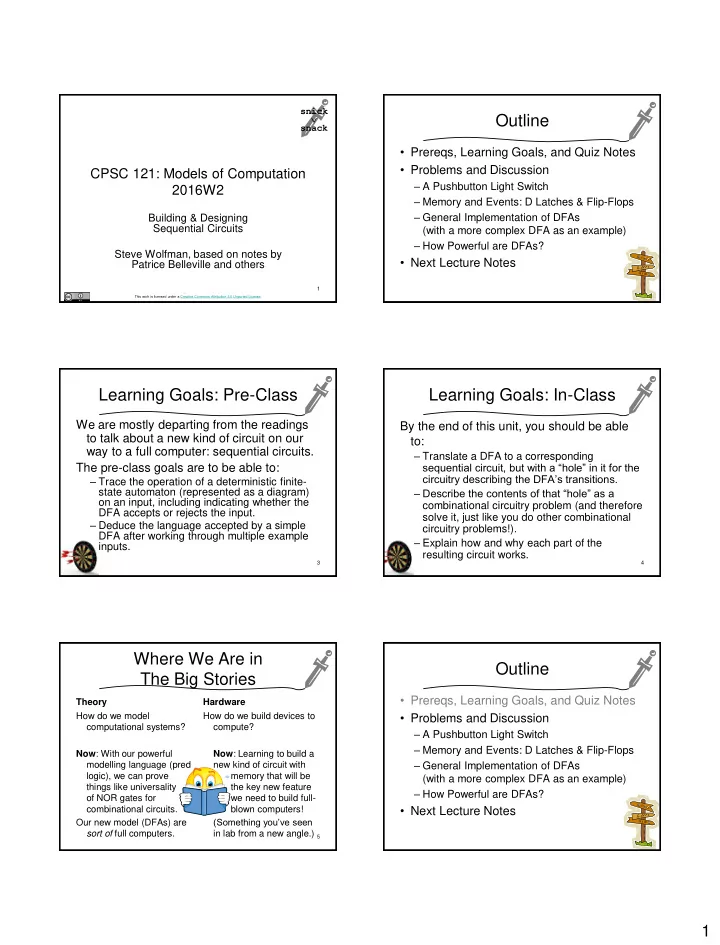

CPSC 121: Models of Computation 2016W2

Building & Designing Sequential Circuits Steve Wolfman, based on notes by Patrice Belleville and others

1

This work is licensed under a Creative Commons Attribution 3.0 Unported License.

Outline

- Prereqs, Learning Goals, and Quiz Notes

- Problems and Discussion

– A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs?

- Next Lecture Notes

2

Learning Goals: Pre-Class

We are mostly departing from the readings to talk about a new kind of circuit on our way to a full computer: sequential circuits. The pre-class goals are to be able to:

– Trace the operation of a deterministic finite- state automaton (represented as a diagram)

- n an input, including indicating whether the

DFA accepts or rejects the input. – Deduce the language accepted by a simple DFA after working through multiple example inputs.

3

Learning Goals: In-Class

By the end of this unit, you should be able to:

– Translate a DFA to a corresponding sequential circuit, but with a “hole” in it for the circuitry describing the DFA’s transitions. – Describe the contents of that “hole” as a combinational circuitry problem (and therefore solve it, just like you do other combinational circuitry problems!). – Explain how and why each part of the resulting circuit works.

4

Where We Are in The Big Stories

Theory How do we model computational systems? Now: With our powerful modelling language (pred logic), we can prove things like universality

- f NOR gates for

combinational circuits. Our new model (DFAs) are sort of full computers. Hardware How do we build devices to compute? Now: Learning to build a new kind of circuit with memory that will be the key new feature we need to build full- blown computers! (Something you’ve seen in lab from a new angle.) 5

Outline

- Prereqs, Learning Goals, and Quiz Notes

- Problems and Discussion

– A Pushbutton Light Switch – Memory and Events: D Latches & Flip-Flops – General Implementation of DFAs (with a more complex DFA as an example) – How Powerful are DFAs?

- Next Lecture Notes

6