1

- 1

2: Archit ect ural Underpinnings and Applicat ion Requirement s

1/ 11/ 2004 8:59 PM

- 2

OS Layer

Remember OS is a layer bet ween t he under lying

har dwar e and applicat ion demands

OS f unct ionalit y det er mined by bot h

Feat ur es of t he har dwar e Demands of applicat ions

Applicat ions Operat ing Syst ems Hardware

- 3

Raw Mat erials

What does t he OS have t o work t o provide

an ef f icient , f air, convenient , secure comput ing plat f orm?

Raw har dwar e

CPU ar chit ect ur e (inst r uct ion set s, r egist er s,

busses, caches, DMA cont r oller s, et c.)

Per ipher als (CD-ROMs, disk dr ives, net wor k

int er f aces, et c.)

- 4

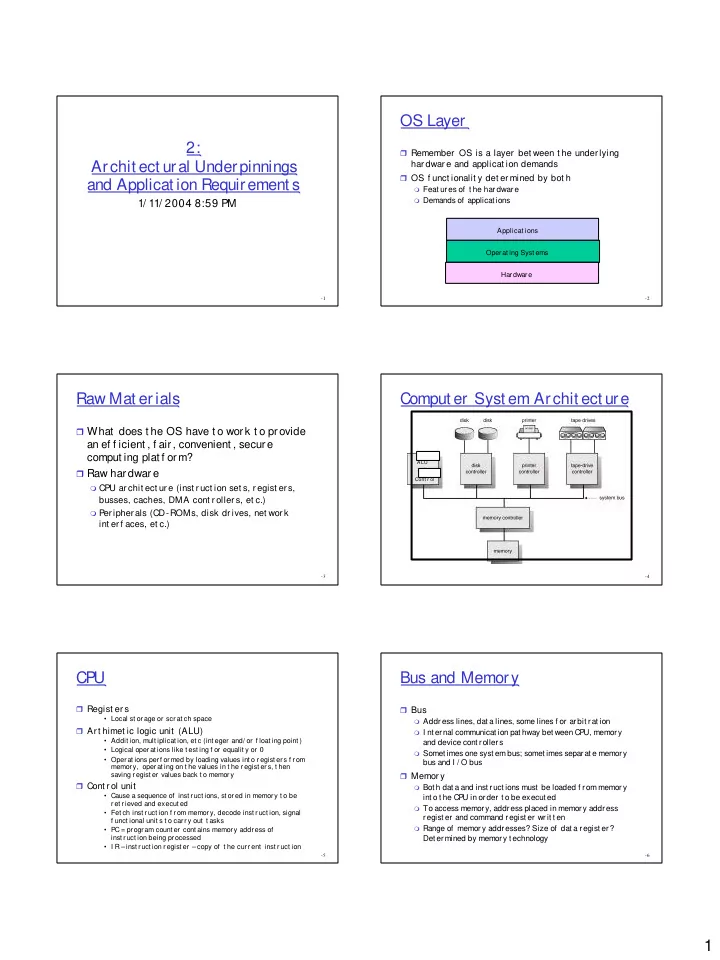

Comput er Syst em Archit ect ure

ALU Cont r ol

- 5

CP U

Regist er s

- Local st or age or scr at ch space

Ar t himet ic logic unit (ALU)

- Addit ion, mult iplicat ion, et c (int eger and/ or f loat ing point )

- Logical oper at ions like t est ing f or equalit y or 0

- Operat ions perf ormed by loading values int o regist ers f rom

memory, operat ing on t he values in t he regist ers, t hen saving regist er values back t o memory

Cont r ol unit

- Cause a sequence of inst ruct ions, st ored in memory t o be

ret rieved and execut ed

- Fet ch inst r uct ion f r om memor y, decode inst r uct ion, signal

f unct ional unit s t o car r y out t asks

- PC = program count er cont ains memory address of

inst ruct ion being processed

- I R – inst ruct ion regist er – copy of t he cur r ent inst r uct ion

- 6

Bus and Memory

Bus

Address lines, dat a lines, some lines f or arbit rat ion I nt ernal communicat ion pat hway bet ween CP

U, memory and device cont rollers

Somet imes one syst em bus; somet imes separat e memory

bus and I / O bus Memor y

Bot h dat a and inst ruct ions must be loaded f rom memory

int o t he CP U in order t o be execut ed

To access memory, address placed in memory address

regist er and command regist er writ t en

Range of memory addresses? Size of dat a regist er?