NOW Handout Page 1

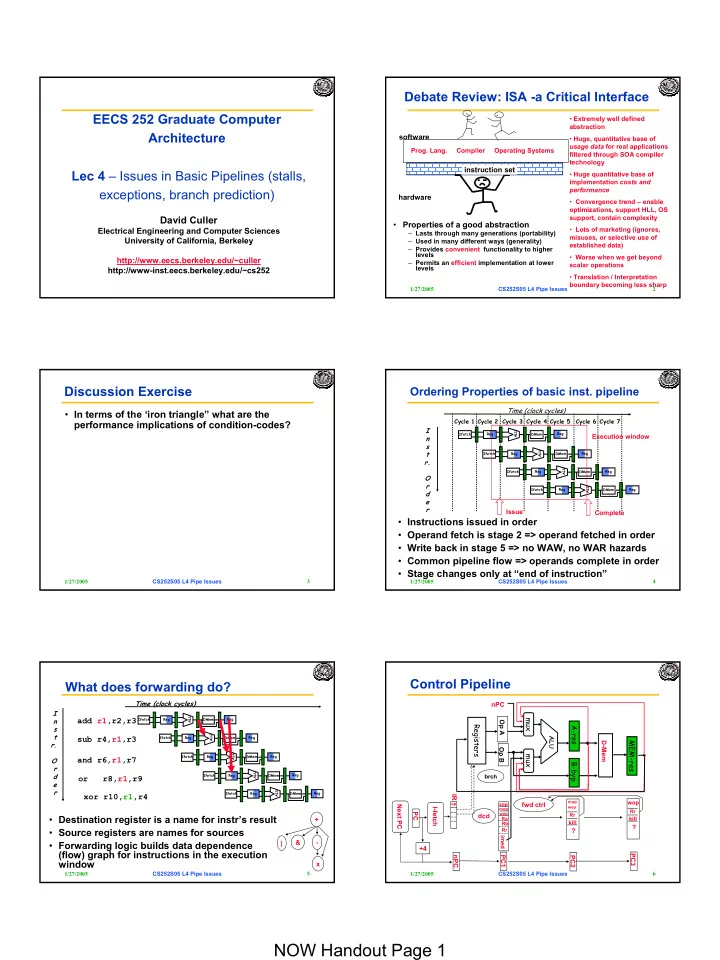

EECS 252 Graduate Computer Architecture Lec 4 – Issues in Basic Pipelines (stalls, exceptions, branch prediction)

David Culler

Electrical Engineering and Computer Sciences University of California, Berkeley http://www.eecs.berkeley.edu/~culler http://www-inst.eecs.berkeley.edu/~cs252

1/27/2005 CS252S05 L4 Pipe Issues 2

Debate Review: ISA -a Critical Interface

instruction set software hardware

- Properties of a good abstraction

– Lasts through many generations (portability) – Used in many different ways (generality) – Provides convenient functionality to higher levels – Permits an efficient implementation at lower levels

- Prog. Lang. Compiler Operating Systems

- Extremely well defined

abstraction

- Huge, quantitative base of

usage data for real applications filtered through SOA compiler technology

- Huge quantitative base of

implementation costs and performance

- Convergence trend – enable

- ptimizations, support HLL, OS

support, contain complexity

- Lots of marketing (ignores,

misuses, or selective use of established data)

- Worse when we get beyond

scalar operations

- Translation / Interpretation

boundary becoming less sharp

1/27/2005 CS252S05 L4 Pipe Issues 3

Discussion Exercise

- In terms of the ‘iron triangle” what are the

performance implications of condition-codes?

1/27/2005 CS252S05 L4 Pipe Issues 4

Ordering Properties of basic inst. pipeline

- Instructions issued in order

- Operand fetch is stage 2 => operand fetched in order

- Write back in stage 5 => no WAW, no WAR hazards

- Common pipeline flow => operands complete in order

- Stage changes only at “end of instruction”

I n s t r. O r d e r Time (clock cycles)

Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 6 Cycle 7 Cycle 5

Issue Complete Execution window

1/27/2005 CS252S05 L4 Pipe Issues 5

What does forwarding do?

Time (clock cycles) I n s t r. O r d e r

add r1,r2,r3 sub r4,r1,r3 and r6,r1,r7

- r r8,r1,r9

xor r10,r1,r4

Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg Reg ALU DMem Ifetch Reg

- Destination register is a name for instr’s result

- Source registers are names for sources

- Forwarding logic builds data dependence

(flow) graph for instructions in the execution window

+

- x

& |

1/27/2005 CS252S05 L4 Pipe Issues 6

aop Ra Rb Rr

dcd

mop wop

Control Pipeline

MEM-res A-res

ALU

mux mux Registers

Op A Op B

B-byp

PC IR nPC Next PC I-fetch D-Mem

- p

imed

+4

brch

nPC

mop

Rr

kill

?

wop

wop

Rr

kill

? PC1 PC2 PC3 fwd ctrl