Practical Problems in VLSI Physical Design Multi-level Coarsening (1/11)

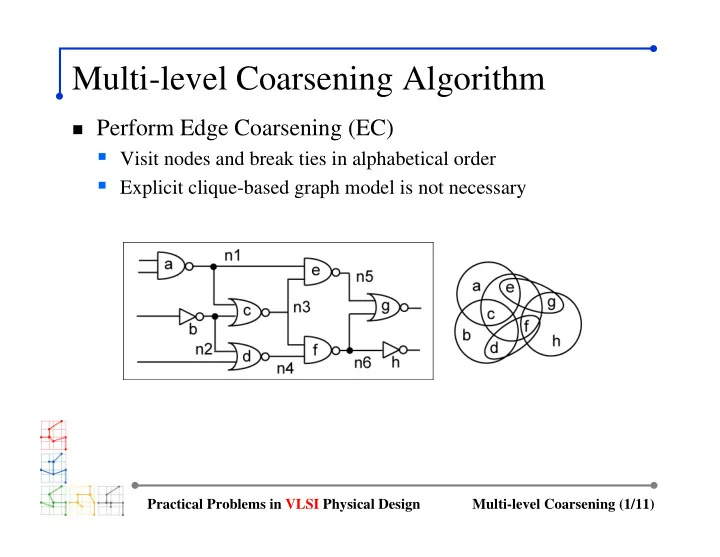

Perform Edge Coarsening (EC)

Multi-level Coarsening Algorithm Perform Edge Coarsening (EC) Visit - - PowerPoint PPT Presentation

Multi-level Coarsening Algorithm Perform Edge Coarsening (EC) Visit nodes and break ties in alphabetical order Explicit clique-based graph model is not necessary Practical Problems in VLSI Physical Design Multi-level Coarsening (1/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (1/11)

Perform Edge Coarsening (EC)

Practical Problems in VLSI Physical Design Multi-level Coarsening (2/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (3/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (4/11)

# of nodes/hyperedges reduced: 4 nodes, 5 hyperedges

Practical Problems in VLSI Physical Design Multi-level Coarsening (5/11)

Initial setup

Practical Problems in VLSI Physical Design Multi-level Coarsening (6/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (7/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (8/11)

# of nodes/hyperedges reduced: 6 nodes, 4 hyperedges

Practical Problems in VLSI Physical Design Multi-level Coarsening (9/11)

Revisit skipped nets during hyperedge coarsening

Practical Problems in VLSI Physical Design Multi-level Coarsening (10/11)

Practical Problems in VLSI Physical Design Multi-level Coarsening (11/11)

# of nodes/hyperedges reduced: 5 nodes, 4 hyperedges