Efficient Utilization of Scratch‐Pad Memory in Preemptive Multi‐Task Systems

Hiroyuki Tomiyama Ritsumeikan University http://hiroyuki.tomiyama‐lab.org/

Motivation

Memory is one of the most energy‐hungry subsystems in

embedded systems

Up to 50% of total energy

Cache improves energy efficiency by reducing off‐chip memory

accesses

Cache is still energy hungry because of

Tag comparison Automatic replacement mechanism Parallel accesses to multiple ways (in high‐performance cache)

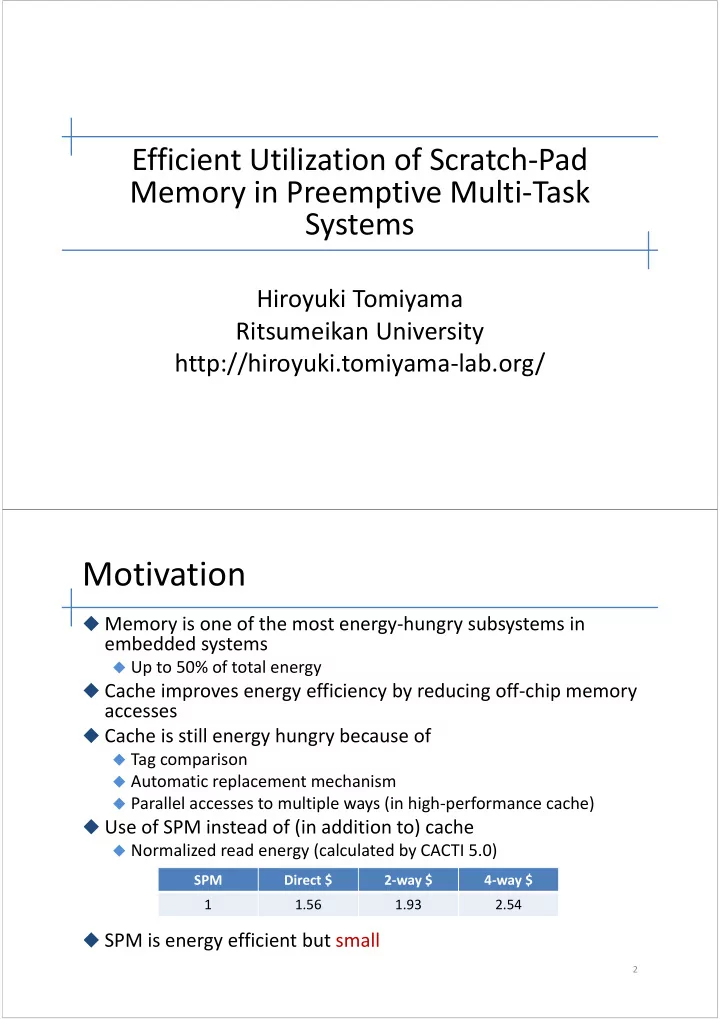

Use of SPM instead of (in addition to) cache

Normalized read energy (calculated by CACTI 5.0)

SPM is energy efficient but small

SPM Direct $ 2‐way $ 4‐way $ 1 1.56 1.93 2.54

2