1

Page 1

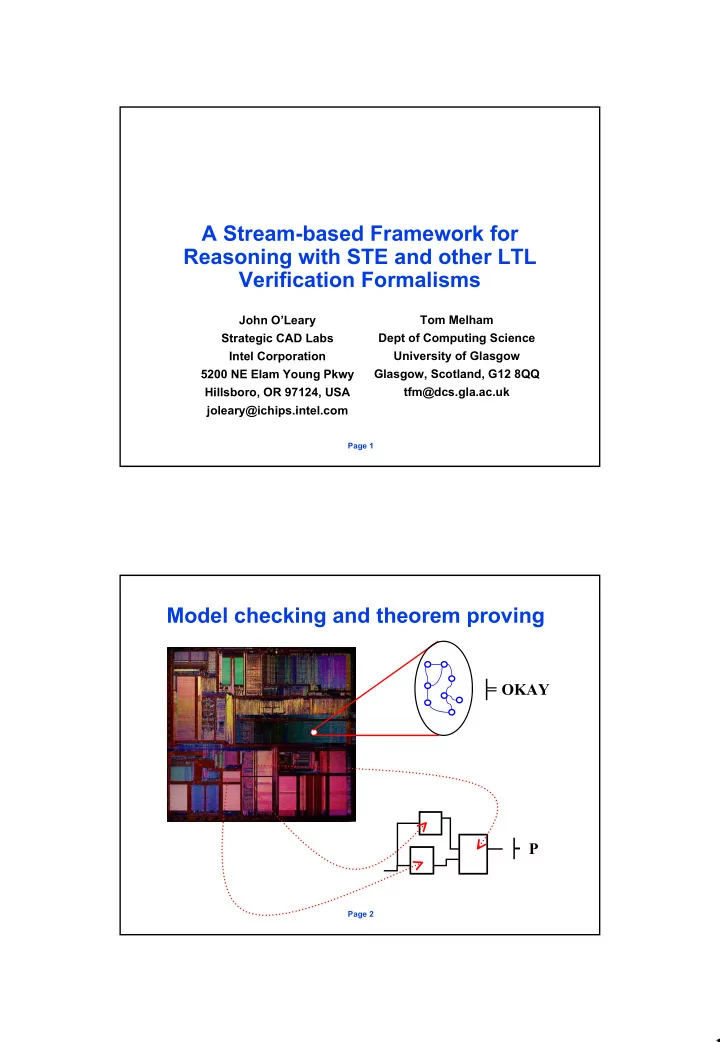

A Stream-based Framework for Reasoning with STE and other LTL Verification Formalisms

John O’Leary Strategic CAD Labs Intel Corporation 5200 NE Elam Young Pkwy Hillsboro, OR 97124, USA joleary@ichips.intel.com Tom Melham Dept of Computing Science University of Glasgow Glasgow, Scotland, G12 8QQ tfm@dcs.gla.ac.uk

Page 2