1/31

Event announcement

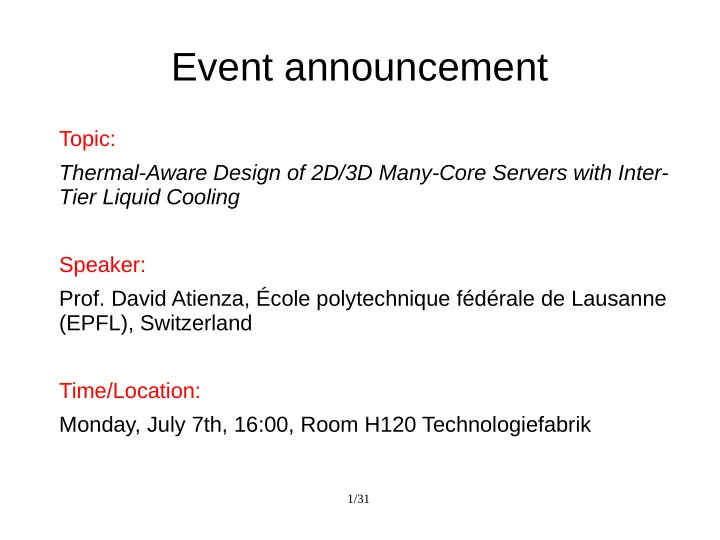

Topic: Thermal-Aware Design of 2D/3D Many-Core Servers with Inter- Tier Liquid Cooling Speaker:

- Prof. David Atienza, École polytechnique fédérale de Lausanne

Event announcement Topic: Thermal-Aware Design of 2D/3D Many-Core - - PowerPoint PPT Presentation

Event announcement Topic: Thermal-Aware Design of 2D/3D Many-Core Servers with Inter- Tier Liquid Cooling Speaker: Prof. David Atienza, cole polytechnique fdrale de Lausanne (EPFL), Switzerland Time/Location: Monday, July 7th, 16:00,

1/31

2/31

OptimSoc http://www.optimsoc.org/ DFG SPP 1500 Dependable Embedded Systems http://spp1500.itec.kit.edu/ ZTEX FPGA Module 1.15

src: http://www.ztex.de/usb-fpga-1/usb-fpga-1.15.e.html

interested? volker.wenzel@kit.edu

3/31

4/31

src: http://en.wikipedia.org/wiki/Moore%27s_law

5/31

probabilistic empirical physical Aging Phenomena

src: de.wikipedia.org/wiki/Tesla-Transformator src:de.wikipedia.org/wiki/ Entropie_Thermodynamik

2nd law of thermodynamics

6/31

7/31

src: http://en.wikipedia.org/wiki/Electromigration

8/31

– A constant – j current density – n parameter – Q activation energy in eV – k Boltzmann constant – T temperature in K

9/31

10/31

src:http://en.wikipedia.org/wiki/Threshold_voltage

11/31

2 surface

12/31

– negative gate voltages – at elevated temperatures

parametric degradation

13/31

– breaking of SiH at SiO2/Si

substrate interface

– H diffuses away

– interface traps

(permanent traps)

– oxide traps

(can recover)

src:http://www.iue.tuwien.ac.at/phd/entner/ Quiz: How could you check if the hydrogen at the Si surface is really responsible for NBTI?

14/31

src: [Schro04]

15/31

– initially quick degradation

16/31

17/31

– voltage stress – signal probability – temperature Vth shift [V] Time

Stress Recovery

Vg [V]

18/31

src:http://www.iue.tuwien.ac.at/phd/entner/node34.html

19/31

src:http://www.iue.tuwien.ac.at/phd/entner/node34.html

20/31

src:http://www.iue.tuwien.ac.at/phd/entner/node34.html

21/31

– supply voltage – channel geometry src: http://www.iue.tuwien.ac.at/phd/entner

22/31

– „hot electrons“ – „lucky electrons“ – electrons w/ high

23/31

– dielectric thickness – manufacturing quality of gate oxide

src:images.nationalgeographic.com

24/31

src: https://nanohub.org/resources/17208/download/2013.03.01-ECE695A-L21.pdf BINGO!

25/31

26/31

27/31

28/31

src: https://nanohub.org/resources/17208/download/2013.03.01-ECE695A-L21.pdf

29/31

src: http://de.wikipedia.org/wiki/Metall-Oxid-Halbleiter-Feldeffekttransistor

30/31

31/31