Jakob Engblom, PhD Jakob Engblom, PhD

Uppsala Uppsala Unive University rsity & Virtutech Inc. & Virtutech Inc.

jakob.engblom@it.uu.se jakob.engblom@it.uu.se jakob@virtutech.com jakob@virtutech.com

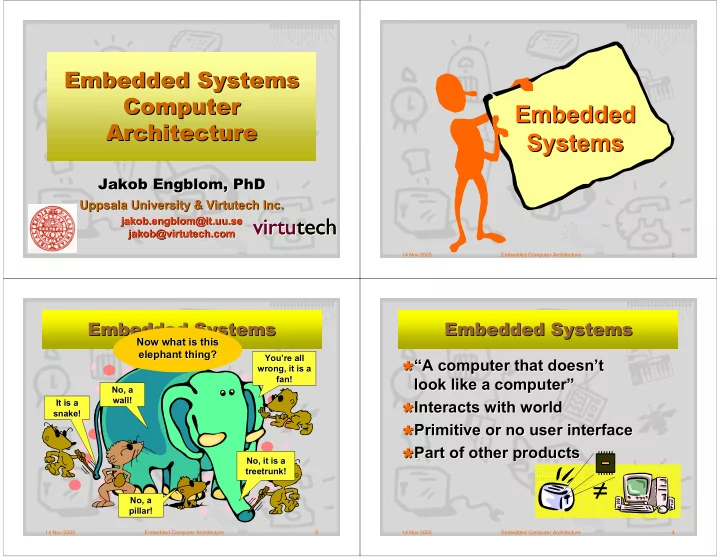

Embedded Embedded Systems Systems Computer Computer Architecture Architecture

tech virtutech virtutech virtutech virtu

14 Nov 2003 Embedded Computer Architecture 2

Embedded Embedded Systems Systems

14 Nov 2003 Embedded Computer Architecture 3

Embedded Systems Embedded Systems

It is a It is a snake snake! ! No, a No, a wall wall! ! No, a No, a pillar! pillar! No, it is a No, it is a treetrunk treetrunk! ! You You’ ’re re all all wrong wrong, it is a , it is a fan! fan!

Now what Now what is this is this elephant thing elephant thing? ?

14 Nov 2003 Embedded Computer Architecture 4

Embedded Systems Embedded Systems

- “

“A computer that doesn A computer that doesn’ ’t t look like a computer look like a computer” ”

- Interacts with world

Interacts with world

- Primitive or no user interface

Primitive or no user interface

- Part of other products