1

CALTECH CS137 Fall2005 -- DeHon 1

CS137: Electronic Design Automation

Day 12: October 28, 2005 Covering and Retiming

CALTECH CS137 Fall2005 -- DeHon 2

Previously

- Cover (map) LUTs for minimum delay

– solve optimally

- Retiming for minimum clock period

– solve optimally

CALTECH CS137 Fall2005 -- DeHon 3

Today

- Solving cover/retime separately not

- ptimal

- Cover+retime

CALTECH CS137 Fall2005 -- DeHon 4

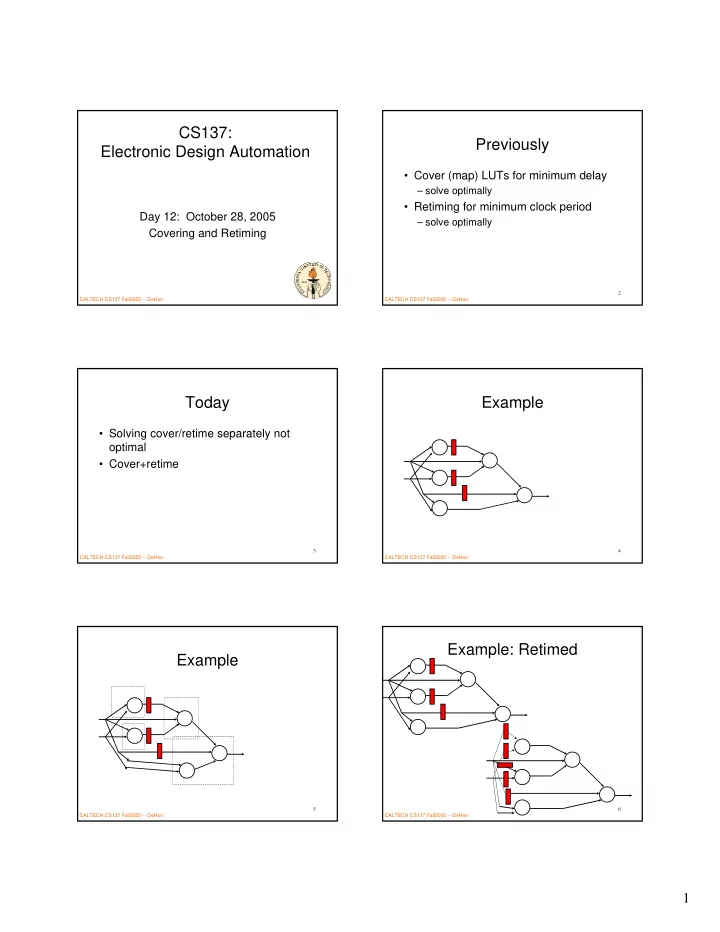

Example

CALTECH CS137 Fall2005 -- DeHon 5

Example

CALTECH CS137 Fall2005 -- DeHon 6