1

Giuseppe Bianchi

Data Plane Programmability the next step in SDN

Giuseppe Bianchi CNIT / University of Roma Tor Vergata

Credits to:

- M. Bonola, A. Capone, C. Cascone, S. Pontarelli, D. Sanvito,

- M. Spaziani Brunella, V. Bruschi

EU Support:

Beba

BEhavioural BAsed forwarding

Giuseppe Bianchi

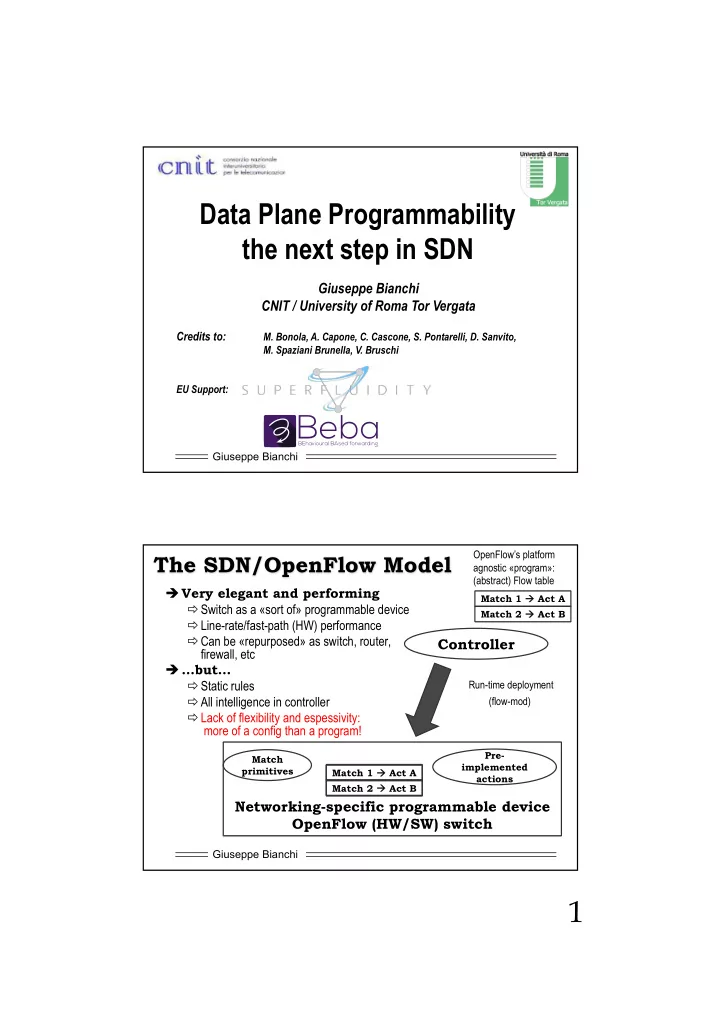

The SDN/OpenFlow Model

Networking-specific programmable device OpenFlow (HW/SW) switch

Match 1 à Act A Match 2 à Act B

(flow-mod)

Pre- implemented actions Match primitives

Controller

Run-time deployment OpenFlow’s platform agnostic «program»: (abstract) Flow table

Match 1 à Act A Match 2 à Act B Not yet «programmed»

è Very elegant and performing ðSwitch as a «sort of» programmable device ðLine-rate/fast-path (HW) performance ðCan be «repurposed» as switch, router, firewall, etc è …but… ðStatic rules ðAll intelligence in controller ðLack of flexibility and espessivity: more of a config than a program!