1

CS252 Graduate Computer Architecture Lecture 20

Vector Processing => Multimedia

David E. Culler Many slides due to Christ of oros E. Kozyrakis

CS252/ Culler Lec 20. 2 4/ 9/ 02

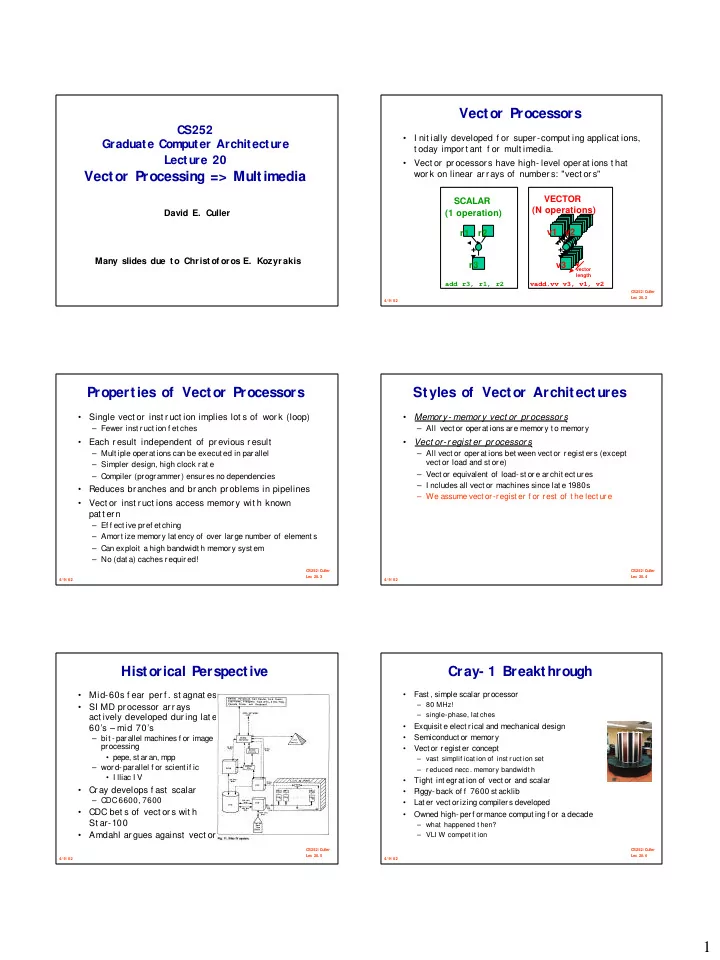

Vector Processors

- I nit ially developed f or super -comput ing applicat ions,

t oday impor t ant f or mult imedia.

- Vect or pr ocessor s have high- level oper at ions t hat

wor k on linear ar r ays of number s: "vect or s" + r1 r2 r3

add r3, r1, r2

SCALAR (1 operation) v1 v2 v3 +

vector length

vadd.vv v3, v1, v2

VECTOR (N operations)

CS252/ Culler Lec 20. 3 4/ 9/ 02

Properties of Vector Processors

- Single vect or inst r uct ion implies lot s of wor k (loop)

– Fewer inst ruct ion f et ches

- Each r esult independent of pr evious r esult

– Mult iple operat ions can be execut ed in parallel – Simpler design, high clock rat e – Compiler (programmer) ensures no dependencies

- Reduces br anches and br anch pr oblems in pipelines

- Vect or inst r uct ions access memor y wit h known

pat t ern

– Ef f ect ive pref et ching – Amort ize memory lat ency of over large number of element s – Can exploit a high bandwidt h memory syst em – No (dat a) caches required!

CS252/ Culler Lec 20. 4 4/ 9/ 02

Styles of Vector Architectures

- Memory- memor y vect or pr ocessor s

– All vect or operat ions are memory t o memory

- Vect or-r egist er pr ocessor s

– All vect or operat ions bet ween vect or regist ers (except vect or load and st ore) – Vect or equivalent of load- st ore archit ect ures – I ncludes all vect or machines since lat e 1980s – We assume vect or-regist er f or rest of t he lect ure

CS252/ Culler Lec 20. 5 4/ 9/ 02

Historical Perspective

- Mid-60s f ear per f . st agnat es

- SI MD pr ocessor ar r ays

act ively developed dur ing lat e 60’s – mid 70’s

– bit - parallel machines f or image processing

- pepe, st aran, mpp

– wor d- parallel f or scient if ic

- I lliac I V

- Cr ay develops f ast scalar

– CDC 6600, 7600

- CDC bet s of vect or s wit h

St ar-100

- Amdahl ar gues against vect or

CS252/ Culler Lec 20. 6 4/ 9/ 02

Cray- 1 Breakthrough

- Fast , simple scalar processor

– 80 MHz! – single-phase, lat ches

- Exquisit e elect rical and mechanical design

- Semiconduct or memory

- Vect or regist er concept

– vast simplif icat ion of inst ruct ion set – r educed necc. memory bandwidt h

- Tight int egrat ion of vect or and scalar

- P

iggy- back of f 7600 st acklib

- Lat er vect orizing compilers developed

- Owned high- perf ormance comput ing f or a decade