1

Synthesis of sequential circuits

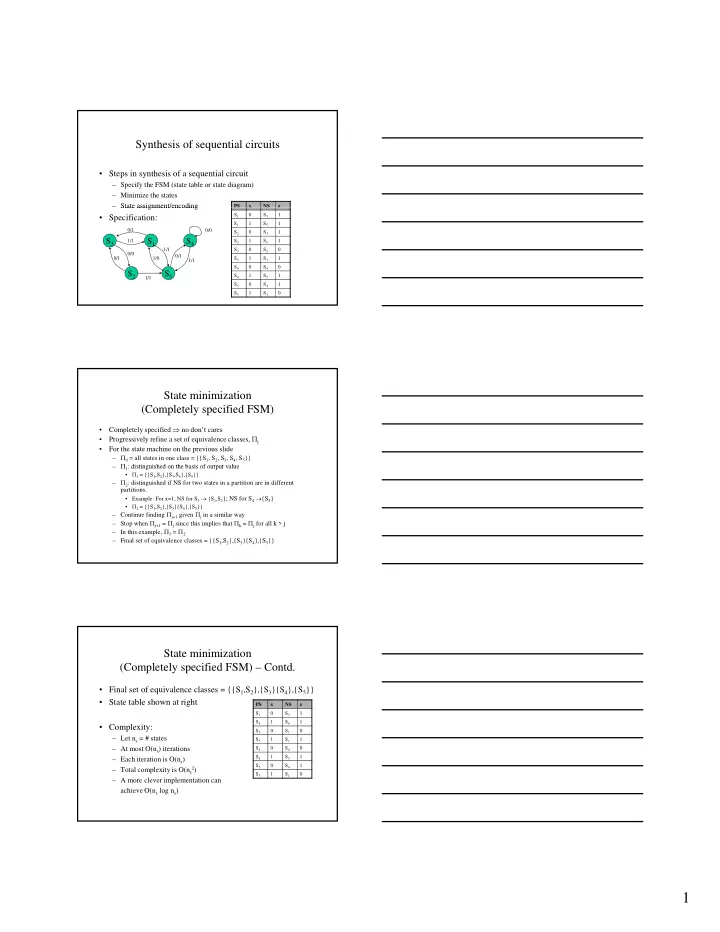

- Steps in synthesis of a sequential circuit

– Specify the FSM (state table or state diagram) – Minimize the states – State assignment/encoding

PS x NS z

State assignment/encoding

- Specification:

S3 S1 S2 S5 S4

0/0 1/1 0/1 1/1 1/0 1/1 0/0 0/1 1/1 0/1 S1 S3 1 S1 1 S5 1 S2 S3 1 S2 1 S5 1 S3 S2 S3 1 S1 1 S4 S4 S4 1 S5 1 S5 S4 1 S5 1 S1

State minimization (Completely specified FSM)

- Completely specified no don’t cares

- Progressively refine a set of equivalence classes, j

- For the state machine on the previous slide

– 0 = all states in one class = {{S1, S2, S3, S4, S5}} : distinguished on the basis of output value – 1: distinguished on the basis of output value

- 1 = {{S1,S2},{S3,S4},{S5}}

– 2: distinguished if NS for two states in a partition are in different partitions.

- Example: For x=1, NS for S3 {S1,S2}; NS for S4 {S5}

- 2 = {{S1,S2},{S3}{S4},{S5}}

– Continue finding j+1 given j in a similar way – Stop when j+1 = j since this implies that k = j for all k > j – In this example, 3 = 2 – Final set of equivalence classes = {{S1,S2},{S3}{S4},{S5}}

State minimization (Completely specified FSM) – Contd.

- Final set of equivalence classes = {{S1,S2},{S3}{S4},{S5}}

- State table shown at right

PS x NS z S1 S3 1 S1 1 S5 1

- Complexity:

– Let ns = # states – At most O(ns) iterations – Each iteration is O(ns) – Total complexity is O(ns

2)

– A more clever implementation can achieve O(ns log ns)

1 5S3 S1 S3 1 S1 1 S4 S4 S4 1 S5 1 S5 S4 1 S5 1 S1