Gary Tyson 1

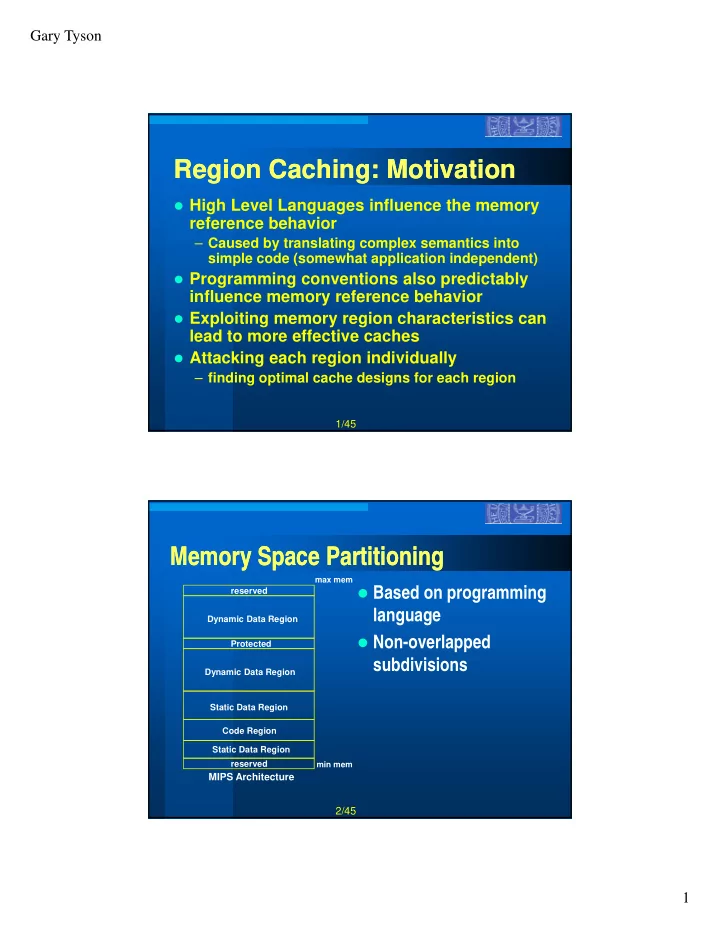

Region Caching: Motivation Region Caching: Motivation

High Level Languages influence the memory

f b h i reference behavior

– Caused by translating complex semantics into simple code (somewhat application independent)

Programming conventions also predictably

influence memory reference behavior

Exploiting memory region characteristics can

1/45

p g y g lead to more effective caches

Attacking each region individually

– finding optimal cache designs for each region

Memory Space Partitioning Memory Space Partitioning

Based on programming

reserved max mem

language

Non-overlapped

subdivisions

Protected Static Data Region Dynamic Data Region Dynamic Data Region

2/45

reserved min mem

MIPS Architecture

Static Data Region Code Region