Central R&D

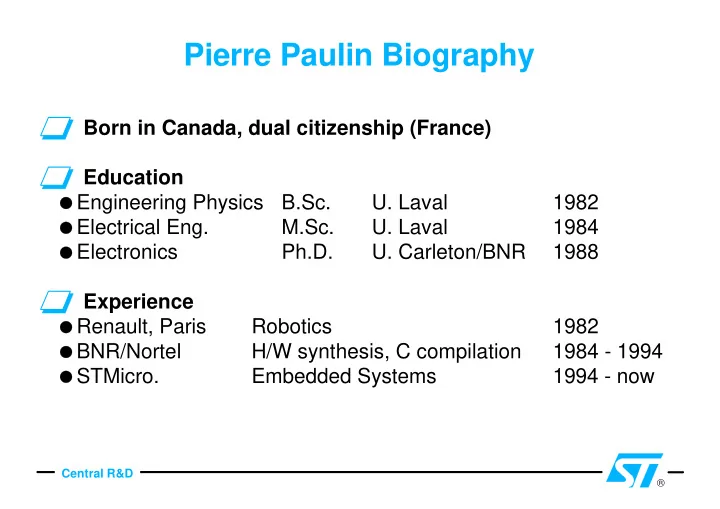

Born in Canada, dual citizenship (France) Education Engineering Physics B.Sc.

- U. Laval

1982 Electrical Eng. M.Sc.

- U. Laval

1984 Electronics Ph.D.

- U. Carleton/BNR

1988 Experience Renault, Paris Robotics 1982 BNR/Nortel H/W synthesis, C compilation 1984 - 1994 STMicro. Embedded Systems 1994 - now