1

DAC2000 (C) Monterey Design Systems 1

Physical Design Closure Physical Design Closure

DAC 2000

Olivier Coudert

Monterey Design System

DAC2000 (C) Monterey Design Systems 2

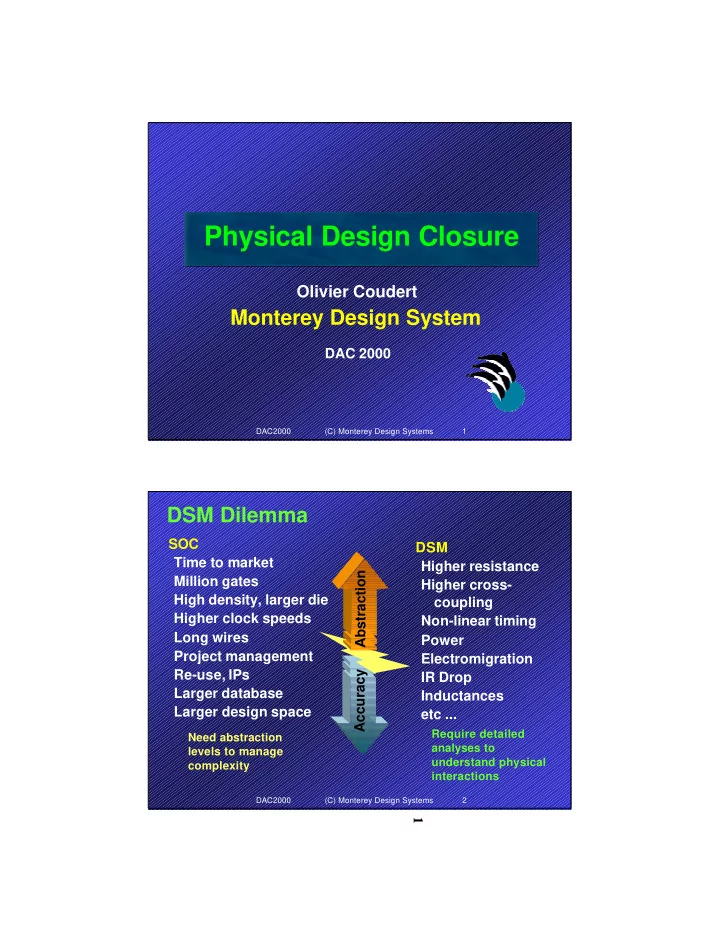

DSM Dilemma

SOC Time to market Million gates High density, larger die Higher clock speeds Long wires Project management Re-use, IPs Larger database Larger design space

Need abstraction levels to manage complexity Require detailed analyses to understand physical interactions