SLIDE 1

1

Fall2001 1

MachineArchitecture

CS217

Fall2001 2

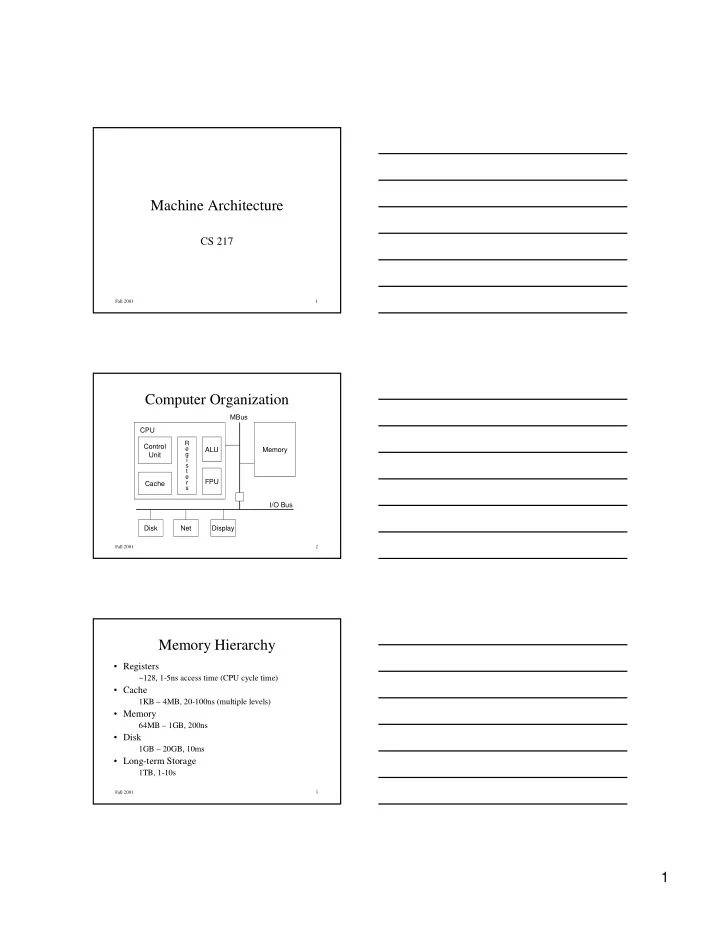

ComputerOrganization

Control Unit Cache

R e g i s t e r s

ALU FPU CPU Memory Disk Net Display MBus I/OBus

Fall2001 3

MemoryHierarchy

- Registers

~128,1-5nsaccesstime(CPUcycletime)

- Cache

1KB– 4MB,20-100ns(multiplelevels)

- Memory

64MB– 1GB,200ns

- Disk

1GB– 20GB,10ms

- Long-termStorage